PyCoRAM: Python-Verilog高位合成とメモリ抽象化によるFPGAアクセラレータ向けIPコア開発フレームワーク (FPGAX #05)

- 1. PyCoRAM Python-Verilog高位合成とメモリ抽象化による FPGAアクセラレータ向け IPコア開発フレームワーク 高前田(山崎) 伸也 (@shtaxxx) 東京工業大学 大学院情報理工学研究科 日本学術振興会 特別研究員 (DC1) 2014年3月10日 第5回FPGAX@西新宿ニフティ

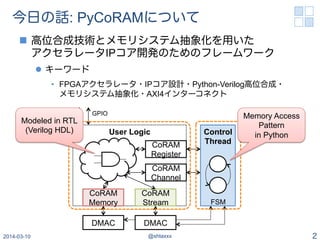

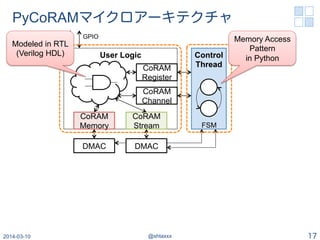

- 2. 今日の話: PyCoRAMについて n 高位合成技術とメモリシステム抽象化を用いた アクセラレータIPコア開発のためのフレームワーク l キーワード • FPGAアクセラレータ・IPコア設計・Python-Verilog高位合成・ メモリシステム抽象化・AXI4インターコネクト 2014-03-10 @shtaxxx 2 User I/O User Logic CoRAM Channel CoRAM Register Control Thread DMAC CoRAM Memory DMAC CoRAM Stream FSM GPIO Modeled in RTL (Verilog HDL) Memory Access Pattern in Python

- 3. PyCoRAM and Pyverilog are released for public! n PyCoRAM l http://shtaxxx.github.io/PyCoRAM/ n Pyverilog l http://shtaxxx.github.io/Pyverilog/ 2014-03-10 @shtaxxx 3

- 5. FPGA as SoC (System-on-Chip) n 沢山のパーツを単一FPGA上に集積しSoCとして利用 l CPUコア • Microblaze (ソフトマクロ) • Cortex-A9 (ハードマクロ) l アクセラレータロジック • 普通のRTLでモデリング – Verilog HDL, VHDL • 新しい言語でモデリング – Bluespec, AutoESL, Chisel, … l DDR3 DRAM l PCI-Express l Ethernet, … 2014-03-10 @shtaxxx 5 FPGA CPU HW Acc DRAM I/F Ether PCI-E Interconnect HW Acc

- 6. アプリケーションのポータビリティ n どうやって様々なプラットフォームをサポートするか? l プラットフォーム毎に特性が違うL • ロジックサイズ・メモリサイズ・ メモリインターフェース・I/O・・・ 2014-03-10 @shtaxxx 6 Digilent Atlys (Xilinx Spartan-6 LX45) Xilinx ML605 (Xilinx Virtex-6 LX240T) ScalableCore System (our FPGA system) (Xilinx Spartan-6 LX16 × 128-node)

- 8. IPコアベースのシステム開発 n IPコアを開発・追加して繋げばシステム完成J l 標準的なインターコネクトでIPコア達を接続 l EDAツールが自動的にインターコネクトと(いくつかの) デバイス依存のインターフェースを生成してくれるから楽ちん 2014-03-10 @shtaxxx 8 Xilinx Platform Studio (XPS) IP-core List Interconnect FPGA CPU HW Acc DRAM I/F Ether PCI-E Interconnect HW Acc DRAM IP-core Instances

- 9. どうやってアクセラレータIPを実装するか? n 普通にHDLでアクセラレータを実装するのは芸が無い l というかいろいろ面倒で嫌だ! • 演算とメモリアクセスのスケジューリングロジック – ダブルバッファリングとか面倒 • メモリシステムの制御回路 – HDLでステートマシンを書くのは面倒だし間違えやすい • デバッグが面倒 l でもパイプラインの振る舞いはサイクルレベルで定義したい • FPGAで性能を出すには高稼働率のパイプラインが重要 – だから計算ロジックはHDLで書きたい – 高位合成だとチューンがイマイチ難しい n 抽象化されたメモリシステムが使えると幸せそう 2014-03-10 @shtaxxx 9 CoRAMメモリアーキテクチャ

- 10. CoRAM [Chung+,FPGA’11] n FPGAアクセラレータのためのメモリ抽象化 l 高位モデルによるメモリ管理でアクセラレータをポータブルに • 計算カーネルとメモリアクセスの分離 • ソフトウェアのモデルによるメモリアクセスパターンの記述 2014-03-10 @shtaxxx 10 HW Kernels (Computing Logics) CoRAM Memory Read Write Manage Control Threads (Memory Access Pattern) CoRAM Channel Read/Write Read/Write Communication FIFOs (Registers) Abstracted On-chip Memories Off-chip Memory

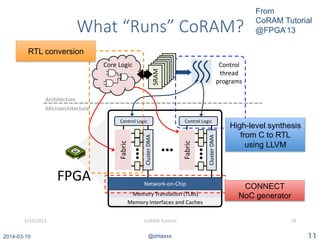

- 11. 2014-03-10 @shtaxxx 11 What “Runs” CoRAM? Memory Translation (TLBs) Architecture Microarchitecture Memory Interfaces and Caches Fabric ClusterDMA Control thread programs Control Logic FPGA SRAM Core Logic Fabric ClusterDMA Control Logic Network-on-Chip 6/19/2013 CoRAM Tutorial 18 From CoRAM Tutorial @FPGA’13 High-level synthesis from C to RTL using LLVM RTL conversion CONNECT NoC generator

- 13. Motivation: CoRAM for Modern EDKs n CoRAMのメモリ抽象化を今時のEDKで使いたい l 標準的なインターコネクト( AMBA AXI4)に繋ぎたい l そうすれば他の普通のIPコアとも簡単に共存できそう 2014-03-10 @shtaxxx 13 Standard On-chip Interconnect CoRAM Abstraction Accelerator logic Standard IP-core Device-dependent Interfaces CPU core Portable application design with CoRAM Cooperation with standard IP-cores

- 14. PyCoRAM [Takamaeda+,CARL’13] n ベンダーEDK向けのPythonベースのCoRAM実装 l 計算カーネルのRTL記述とメモリアクセスパターンの Python記述からAXI4 IPコアを自動合成 l 出来上がったIPコアをEDKでポチポチつなげばシステム完成! n 特徴 l Pythonでのコントロールスレッド記述 • Pythonで簡単にメモリアクセスパターンを記述できる – 独自の高位合成コンパイラでPython記述からVerilog HDLのRTLを合成 l AMBA AXI4インターコネクトのサポート • Xilinx Platform Studio (XPS)などを用いたIPコアベースの開発を支援 l 計算ロジックの複雑なデザインに対応 • ハードウェアデザイン解析・生成のための オープンソースツールキットPyverilogを活用 2014-03-10 @shtaxxx 14

- 15. オリジナルのCoRAMとの比較 CoRAM PyCoRAM Language for Control-Thread C Python Supported Memory Operations (Blocking/Non-Blocking) Read/Write (Blocking/Non-Blocking) Read/Write On-chip Interconnect CONNECT NoC [FPGA’12] AMBA AXI4 FSM Granularity in Control Thread LLVM-IR Python AST Node Generate Statement Support for User logics No Yes Supported FPGAs Xilinx ML605 Altera Terasic DE-4 Any FPGAs supporting AXI Bus # Lines of Code 11,682 lines (w/o CONNECT) 4,947 lines (w/o Pyverilog) 2014-03-10 @shtaxxx 15 FSM: Finite State Machine LLVM-IR: Low Level Virtual Machine Intermediate Representation AST: Abstract Syntax Tree

- 16. PyCoRAMマイクロアーキテクチャ 2014-03-10 @shtaxxx 16 User I/O User Logic CoRAM Channel CoRAM Register Control Thread DMAC CoRAM Memory DMAC CoRAM Stream FSM GPIO

- 17. PyCoRAMマイクロアーキテクチャ 2014-03-10 @shtaxxx 17 User I/O User Logic CoRAM Channel CoRAM Register Control Thread DMAC CoRAM Memory DMAC CoRAM Stream FSM GPIO Modeled in RTL (Verilog HDL) Memory Access Pattern in Python

- 18. PyCoRAMマイクロアーキテクチャの実装 2014-03-10 @shtaxxx 18 PyCoRAM IP AXI4 Interconnect DRAM ControllerFPGA User I/O User Logic CoRAM Channel CoRAM Register Control Thread DMAC AXI I/F CoRAM Memory DMAC AXI I/F CoRAM Stream FSM GPIO

- 19. PyCoRAMにおける開発フロー n 計算カーネルのRTLとPythonでのコントロールスレッド 記述からIPコアパッケージを生成 l 生成されたIPコアは通常のEDAフローで利用可能 2014-03-10 @shtaxxx 19 User-logic (Verilog HDL) Control Threads (Python) Logic Hierarchy Analysis Python-to- Verilog Compilation Control Signal Insertion IP-core Packing (RTL, .mpd, and .pao) IP-core Integration on EDK Synthesis Control Signal Port Addition FPGA Bit File Portable Application Design PyCoRAM Tool-chain Vendor EDA FlowPython-to-Verilog HLS RTL Conversion IP-core generation with AXI4 Interface Top design synthesis with AXI4

- 20. Pythonによるコントロールスレッド n CoRAMオブジェクトに対する処理を記述する l CoRAMメモリ(read/write) • オンチップCoRAMメモリとオフチップDRAM との間のDMA転送によるデータ移動 l CoRAMチャネル(read/write) • ユーザロジックとコントロールスレッド との間のトークンのやりとり 2014-03-10 @shtaxxx 20 def calc_sum(times):� ram = CoramMemory(idx=0, datawidth=32, size=1024)� channel = CoramChannel(idx=0, datawidth=32)� addr = 0� sum = 0� for i in range(times):� ram.write(0, addr, 128)� channel.write(addr)� sum += channel.read()� addr += 128 * (32/8)� print(‘sum=’, sum)� calc_sum(8)� # Transfer (off-chip DRAM to BRAM) # Notification to User-logic # Wait for Notification from User-logic # $display Verilog system task � User I/O User Logic CoRAM Channel Control Thread DMAC CoRAM Memory FSM 0� 1� 2� 3� 4� 5� 6� 7� 8� 9� 10� 11�

- 21. 計算ロジックにおけるCoRAMオブジェクト n CoRAMオブジェクトはブロックRAMやFIFOとして扱う l 一般的なメモリとよく似たインターフェース • CoRAMと外部を接続するインターフェースは自動的に追加される l いくつかのパラメータで特性を指定 • スレッド名,ID,データ幅,アドレス幅,スキャッターギャザー等 2014-03-10 @shtaxxx 21 CoramMemory1P� #(� .CORAM_THREAD_NAME("thread_name"),� .CORAM_ID(0),� .CORAM_ADDR_LEN(ADDR_LEN),� .CORAM_DATA_WIDTH(DATA_WIDTH)� )� inst_memory� (.CLK(CLK),� .ADDR(mem_addr),� .D(mem_d),� .WE(mem_we),� .Q(mem_q)� );� (a) CoRAM Memory CoramChannel� #(� .CORAM_THREAD_NAME("thread_name"),� .CORAM_ID(0),� .CORAM_ADDR_LEN(CHANNEL_ADDR_LEN),� .CORAM_DATA_WIDTH(CHANNEL_DATA_WIDTH)� )� inst_channel� (.CLK(CLK),� .RST(RST),� .D(comm_d),� .ENQ(comm_enq),� .FULL(comm_full),� .Q(comm_q),� .DEQ(comm_deq),� .EMPTY(comm_empty)� );� (b) CoRAM Channel

- 22. サポートされているPyCoRAMオブジェクト n データ置き場(メモリ) l CoramMemory • Block RAM that the data is replaced by the control thread l CoramInStream • Input FIFO from off-chip DRAM l CoramOutStream • Output FIFO to off-chip DRAM n ユーザロジックとコンロールスレッド間のチャネル l CoramChannel • Communication FIFO between user-logic and control-thread l CoramRegister • Communication latch between user-logic and control-thread 2014-03-10 @shtaxxx 22

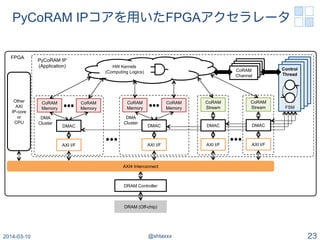

- 23. PyCoRAM IPコアを用いたFPGAアクセラレータ 2014-03-10 @shtaxxx 23 Control Thread FSM AXI4 Interconnect DRAM Controller DRAM (Off-chip) DMAC AXI I/F CoRAM Memory CoRAM Memory AXI I/F CoRAM Memory CoRAM Memory DMAC DMAC AXI I/F CoRAM Stream DMAC AXI I/F CoRAM Stream CoRAM Channel HW Kernels (Computing Logics) DMA Cluster DMA Cluster FPGA Other AXI IP-core or CPU PyCoRAM IP (Application)

- 24. PyCoRAM IPコアのインターフェース n 標準的なAXI4マスターインターフェースを自動的に付加 2014-03-10 @shtaxxx 24 DMA Controller ・・・ DramAddr BramAddr Size WrEn RdEn Busy Ready Control Thread FSM Deque Empty RdData AlmFull Enque WrData Ready RdEn RdEn Size Addr AXI Master Interface (Protocol Conversion) AXI4 Interconnect WREADY WVALID WDATA BVALID AWREADY AWVALID AWLEN AWADDR RVALID RREADY RDATA ARREADY ARVALID ARLEN ARADDR Write Address Channel Write Data Channel Read Address Channel Read Data Channel HW Kernels (Computing Logic) Addr WrData RdData WrEn CoRAM Memory (BRAM) Addr WrData RdData WrEn Addr WrData RdData WrEn CoRAM Memory (BRAM) Addr WrData RdData WrEn CoRAM Channel Deque Empty RdData AlmFull Enque WrData Deque Empty RdData AlmFull Enque WrData ・・・DMA Cluster

- 26. PyCoRAMにおけるIPコアの作り方 n 2種類のファイルを用意する l Verilog HDL: 計算ロジック l Python: コントロールスレッド(メモリアクセスパターン) n PyCoRAMがIPコアパッケージディレクトリを作成 2014-03-10 @shtaxxx 26 User-logic (Verilog HDL) Control Threads (Python) Logic Hierarchy Analysis Python-to- Verilog Compilation Control Signal Insertion IP-core Packing (RTL, .mpd, and .pao) IP-core Integration on EDK Synthesis Control Signal Port Addition FPGA Bit File Portable Application Design PyCoRAM Tool-chain Vendor EDA Flow

- 27. 例: 配列の和を求めるアクセラレータ n 1-CoRAM+1-Threadの簡単なハードウェア l CoRAMメモリにDRAM(など)からデータを読み込む l コントロールスレッドでオンチップ-オフチップ間のデータ転送 パターンを表現 2014-03-10 @shtaxxx 27 Computing Logic (Verilog HDL) Control Thread (Python) sum CoRAM Memory 0 + Control Logic CoRAM Channel 0 A

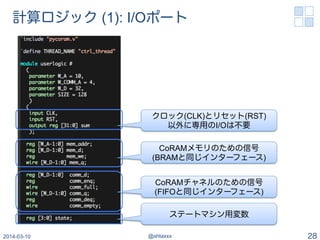

- 28. 計算ロジック (1): I/Oポート 2014-03-10 @shtaxxx 28 クロック(CLK)とリセット(RST) 以外に専用のI/Oは不要 CoRAMメモリのための信号 (BRAMと同じインターフェース) CoRAMチャネルのための信号 (FIFOと同じインターフェース) ステートマシン用変数

- 29. 計算ロジック (2): パイプライン/FSM 2014-03-10 @shtaxxx 29 CoRAMチャネルに書き込み (コントロールスレッドに通知) CoRAMチャネルから読み出し (コントロールスレッドから受信)

- 30. 計算ロジック (3): 子インスタンス 2014-03-10 @shtaxxx 30 CoRAMメモリ (BRAMと同じインターフェース) CoRAMチャネル (FIFOと同じインターフェース)

- 31. コントロールスレッド (Python) 2014-03-10 @shtaxxx 31 ram (CoRAMメモリ)とchannel (CoRAMチャネル)の宣言 CoRAMメモリにDMA転送したり CoRAMチャネルから読んだり書いたり

- 36. PyCoRAMの実装と動作環境 n ピュアなPythonによる実装 l 全体で4947行で実装できたのでコンパクト! • Python-Verilogコンパイラ: 3747行 • RTLトランスレータ: 771行 l Verilog HDLのRTL静的解析にはPyverilogを利用 • Python-based Hardware Design Processing Tool-kit for Verilog HDL • 全体で12664行とかなりコンパクト l コード生成にはJinja2 (テキストテンプレートエンジン)を利用 • テンプレート用テキストファイルが8000行くらい n 動作環境:LinuxかMacを推奨 l Python 3.3 (or later) l Icarus Verilog 0.9.6 (or later) l Jinja2 (2.7 or later) 2014-03-10 @shtaxxx 36

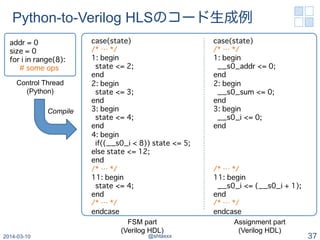

- 37. Python-to-Verilog HLSのコード生成例 2014-03-10 @shtaxxx 37 addr = 0� size = 0� for i in range(8):� # some ops� Control Thread (Python) Compile FSM part (Verilog HDL) Assignment part (Verilog HDL) case(state)� /* … */� 1: begin � state <= 2;� end � 2: begin � state <= 3;� end � 3: begin � state <= 4;� end � 4: begin � if((__s0_i < 8)) state <= 5; � else state <= 12;� end � /* … */� 11: begin � state <= 4;� end � /* … */� endcase� case(state)� /* … */� 1: begin � __s0_addr <= 0;� end � 2: begin � __s0_sum <= 0;� end � 3: begin � __s0_i <= 0;� end � � � � � /* … */� 11: begin � __s0_i <= (__s0_i + 1);� end � /* … */� endcase�

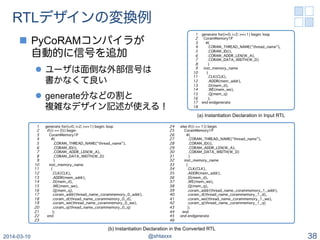

- 38. RTLデザインの変換例 n PyCoRAMコンパイラが 自動的に信号を追加 l ユーザは面倒な外部信号は 書かなくて良い l generate文などの割と 複雑なデザイン記述が使える! 2014-03-10 @shtaxxx 38 generate for(i=0; i<2; i=i+1) begin: loop� CoramMemory1P� #(� .CORAM_THREAD_NAME("thread_name"),� .CORAM_ID(i),� .CORAM_ADDR_LEN(W_A),� .CORAM_DATA_WIDTH(W_D)� )� inst_memory_name� (� .CLK(CLK),� .ADDR(mem_addr),� .D(mem_d),� .WE(mem_we),� .Q(mem_q)� );� end endgenerate� 1� 2� 3� 4� 5� 6� 7� 8� 9� 10� 11� 12� 13� 14� 15� 16� 17� 18� (a) Instantiation Declaration in Input RTL generate for(i=0; i<2; i=i+1) begin: loop� if((i == 0)) begin � CoramMemory1P� #(� .CORAM_THREAD_NAME("thread_name"),� .CORAM_ID(i),� .CORAM_ADDR_LEN(W_A),� .CORAM_DATA_WIDTH(W_D)� )� inst_memory_name� (� .CLK(CLK),� .ADDR(mem_addr),� .D(mem_d),� .WE(mem_we),� .Q(mem_q),� .coram_addr(thread_name_corammemory_0_addr),� .coram_d(thread_name_corammemory_0_d),� .coram_we(thread_name_corammemory_0_we),� .coram_q(thread_name_corammemory_0_q)� );� end � 1� 2� 3� 4� 5� 6� 7� 8� 9� 10� 11� 12� 13� 14� 15� 16� 17� 18� 19� 20� 21� 22� 23� 24� 25� 26� 27� 28� 29� 30� 31� 32� 33� 34� 35� 36� 37� 38� 39� 40� 41� 42� 43� 44� 45� 46� else if((i == 1)) begin � CoramMemory1P� #(� .CORAM_THREAD_NAME("thread_name"),� .CORAM_ID(i),� .CORAM_ADDR_LEN(W_A),� .CORAM_DATA_WIDTH(W_D)� )� inst_memory_name� (� .CLK(CLK),� .ADDR(mem_addr),� .D(mem_d),� .WE(mem_we),� .Q(mem_q),� .coram_addr(thread_name_corammemory_1_addr),� .coram_d(thread_name_corammemory_1_d),� .coram_we(thread_name_corammemory_1_we),� .coram_q(thread_name_corammemory_1_q)� );� end� end endgenerate� (b) Instantiation Declaration in the Converted RTL

- 39. Pyverilog: Python-based Hardware Design Processing Tool-kit for Verilog HDL 2014-03-10 @shtaxxx 39 Module Analyzer Syntax Analyzer Lexical Analyzer AST Signal Analyzer Bind Analyzer Dataflow State Machine Pattern Matcher Control-flow Optimizer Code Generator Active Condition Analyzer Visualizer Verilog HDL Code module TOP (input CLK, input RST, output rslt, … Graphical Output Verilog HDL Code module TOP (input CLK, input RST, output rslt, … Parser Dataflow Analyzer Control-flow Analyzer Input Output AST

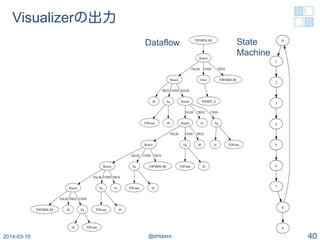

- 40. Visualizerの出力 2014-03-10 @shtaxxx 40 Dataflow State Machine

- 42. 評価 n 評価項目: メモリバンド幅利用率 l メモリ抽象化の下でも高いメモリ性能を達成できることを示す n セットアップ l FPGAボード2種 • Digilent Atlys – Spartan-6 LX45 – DDR2-800 DRAM 128MB (1.2GB/s*) – AXI4 128-bit, 100MHz (1.6GB/s) • Xilinx ML605 – Virtex-6 LX240T – DDR3-800 DRAM 512MB (6.4GB/s) – AXI4 256-bit, 200MHz (6.4GB/s) l EDK • Xilinx Platform Studio (14.6) 2014-03-10 @shtaxxx 42 Xilinx ML605 (Xilinx Virtex-6 LX240T) Digilent Atlys (Xilinx Spartan-6 LX45) *300MHz動作のため

- 43. 評価用アプリケーション n Array-sum: 配列の和を求める l 2つのCoRAMメモリをダブルバッファで利用 l SIMD幅 (=同時に計算する要素数) を変化させてその影響を観測 • 4, 8, 16, 32, 64 (bytes) 2014-03-10 @shtaxxx 43 s3 + s2 + s1 + s0 + MUX D[0]D[1]D[2]D[3]D[0]D[1]D[2]D[3] sum + MUX D[3] D[2] D[1] D[0] Output CoRAM Memory 0 CoRAM Memory 1 from DMA Controller 0 from DMA Controller 1

- 44. 結果:メモリバンド幅利用率 n 結構良い感じでメモリバンド幅を使えている l Atlys: 85.5% (@ 16-byte) l ML605: 84.9% (@ 64-byte) n 100%使い切れていない理由 l 各DMACのトランザクションがシーケンシャルになっているから • 結果,メモリアクセスレイテンシが性能にダイレクトに影響 2014-03-10 @shtaxxx 44 0 0.2 0.4 0.6 0.8 1 4 8 16 32 64 BandwidthUtilization SIMD size [byte] 0 0.2 0.4 0.6 0.8 1 4 8 16 32 BandwidthUtilization SIMD size [byte] Atlys (Spartan-6) ML605 (Virtex-6)

- 46. The 1st IPSJ SIG-ARC High-Performance Processor Design Contest (2014年1月@東工大) n 競技内容 l 指定のFPGAボード上に 指定のアプリケーションを処理可能な 計算機システムを実装し処理時間を競う • FPGAボード: Digilent Atlys – FPGA: Xilinx Spartan-6 LX45, DRAM: DDR2-800 (1.6GB/s) n ルールをよく読む 2014-03-10 @shtaxxx 46 速ければいい!

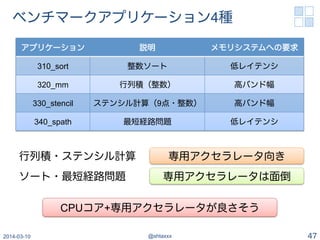

- 47. ベンチマークアプリケーション4種 2014-03-10 @shtaxxx 47 アプリケーション 説明 メモリシステムへの要求 310_sort 整数ソート 低レイテンシ 320_mm 行列積(整数) 高バンド幅 330_stencil ステンシル計算(9点・整数) 高バンド幅 340_spath 最短経路問題 低レイテンシ CPUコア+専用アクセラレータが良さそう 専用アクセラレータ向き行列積・ステンシル計算 ソート・最短経路問題 専用アクセラレータは面倒

- 48. 決勝用FPGAアクセラレータ n 構成: 6段MIPSコア+UARTローダー+アクセラレータ2種 l DRAMとの間のAXI4インターコネクトはXPSが自動的に生成 l 動作周波数: ロジック/AXIバス:100MHz, DRAM:400MHz 2014-03-10 @shtaxxx 48 AXI4 Interconnect (32-bit, Shared-bus) DRAM Controller PyCoRAM Abstraction L1-D Cache (2-way, 32KB, 64bytes/line) 6-stage MIPS-core PyCoRAM Abstraction Memory Loader UART PyCoRAM Abstraction Matrix Multiplication Accelerator PyCoRAM Abstraction 9-point Stencil Accelerator

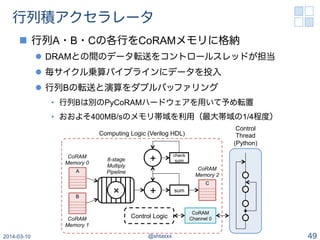

- 49. 行列積アクセラレータ n 行列A・B・Cの各行をCoRAMメモリに格納 l DRAMとの間のデータ転送をコントロールスレッドが担当 l 毎サイクル乗算パイプラインにデータを投入 l 行列Bの転送と演算をダブルバッファリング • 行列Bは別のPyCoRAMハードウェアを用いて予め転置 • おおよそ400MB/sのメモリ帯域を利用(最大帯域の1/4程度) 2014-03-10 @shtaxxx 49 Computing Logic (Verilog HDL) Control Thread (Python) sum CoRAM Memory 0 B × + CoRAM Memory 1 CoRAM Memory 2 Control Logic CoRAM Channel 0 8-stage Multiply PipelineA C check sum+

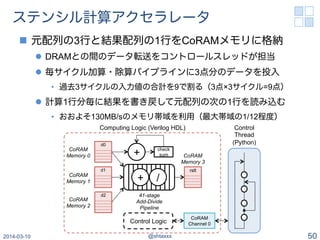

- 50. ステンシル計算アクセラレータ n 元配列の3行と結果配列の1行をCoRAMメモリに格納 l DRAMとの間のデータ転送をコントロールスレッドが担当 l 毎サイクル加算・除算パイプラインに3点分のデータを投入 • 過去3サイクルの入力値の合計を9で割る(3点×3サイクル=9点) l 計算1行分毎に結果を書き戻して元配列の次の1行を読み込む • おおよそ130MB/sのメモリ帯域を利用(最大帯域の1/12程度) 2014-03-10 @shtaxxx 50 Computing Logic (Verilog HDL) Control Thread (Python) CoRAM Memory 0 d1 CoRAM Memory 2 CoRAM Memory 3 Control Logic CoRAM Channel 0 41-stage Add-Divide Pipeline d0 rslt d2 + / + check sum CoRAM Memory 1

- 51. MIPSコア用L1データキャッシュ n データRAMとしてCoRAMメモリを利用 l データリプレイスメントをコントロールスレッドが担当 • キャッシュミス時にコントロールスレッドにリクエストを発行 2014-03-10 @shtaxxx 51 Cache Logic (Verilog HDL) Control Thread (Python) CoRAM Memory 0,1 Control Logic CoRAM Channel 0 D0 D1 MUX Tag0 = Select Tag1 = Write Data Addr Stall Read Data Write Enable Read Enable reg reg reg

- 52. 評価 n 登場選手 l リファレンスデザイン (Ref) l 6段MIPSコア+L1キャッシュ (6-stage) l 6段MIPSコア+L1キャッシュ+アクセラレータ (6-stage+ACC) n アプリケーションデータセット l 予選データセット n FPGA合成ツール l Xilinx Platform Studio 14.6, PlanAhead 14.6 • Optimization goal: Speed, Optimization Effort: High • AXI4 Interconnect: 32-bit Shared bus (Area optimized) n MIPS用ソフトウェアコンパイラ l gcc 4.3.3 (-O3) 2014-03-10 @shtaxxx 52

- 53. 性能 n 全実行時間から転送時間を引いた正味の計算時間を比較 n リファレンスデザインと比較して大幅な速度向上 l 6段MIPSコアのみの構成で平均3.5倍の高速化 l 6段MIPSコア+アクセラレータ2種の構成で 平均13.2倍,最大47.1倍(ステンシル計算)の高速化 2014-03-10 @shtaxxx 53 3.9 1.4 5.9 4.7 3.53.9 35.2 47.1 4.7 13.2 0 5 10 15 20 25 30 35 40 45 50 310_sort 320_mm 330_stencil 340_spath Gmean RelativePerformance 6-stage 6-stage+ACC 14.2 14.2 16.0 20.8 3.6 9.8 2.7 4.4 3.6 0.4 0.3 4.4 0 5 10 15 20 25 310_sort 320_mm 330_stencil 340_spath Time[sec] Ref 6-stage 6-stage+ACC

- 54. ハードウェア使用率 2014-03-10 @shtaxxx 54 0.0% 10.0% 20.0% 30.0% 40.0% 50.0% 60.0% 70.0% 80.0% Slice Reg LUT Peripheral Loader Stencil Acc. MM Acc. L1D-Cache UART MIPS 0 500 1000 1500 2000 2500 3000 3500 4000 4500 5000 L1D-Cache MM Acc. Stencil Acc. Loader AXI I/F DMAC Control Thread User-logic 0 1000 2000 3000 4000 5000 6000 7000 8000 9000 L1D-Cache MM Acc. Stencil Acc. Loader AXI I/F DMAC Control Thread User-logic Slice Reg LUT Entire System Utilization n ユーザロジックと比べてDMACとAXI I/Fの リソース消費量が多い l 整数アプリかつパイプラインが1本 なので相対的に大きく見える n コントロールスレッドのレジスタ消費量が 多い l ステートマシンが巨大なため l 細粒度並列性を抽出しFSMを 小さくすると改善可能? l レジスタは余り気味だから 気にしなくてもいい

- 56. まとめ n PyCoRAM: 高位合成技術とメモリシステム抽象化を用い たアクセラレータIPコア開発のためのフレームワーク n 開発したツール・フレームワークはgithubにて公開中 l PyCoRAM: http://shtaxxx.github.io/PyCoRAM/ l Pyverilog: http://shtaxxx.github.io/Pyverilog/ 2014-03-10 @shtaxxx 56 User I/O User Logic CoRAM Channel CoRAM Register Control Thread DMAC CoRAM Memory DMAC CoRAM Stream FSM GPIO Modeled in RTL (Verilog HDL) Memory Access Pattern in Python

![CoRAM [Chung+,FPGA’11]

n FPGAアクセラレータのためのメモリ抽象化

l 高位モデルによるメモリ管理でアクセラレータをポータブルに

• 計算カーネルとメモリアクセスの分離

• ソフトウェアのモデルによるメモリアクセスパターンの記述

2014-03-10 @shtaxxx 10

HW Kernels

(Computing Logics)

CoRAM

Memory

Read

Write

Manage

Control Threads

(Memory Access

Pattern)

CoRAM

Channel

Read/Write Read/Write

Communication

FIFOs (Registers)

Abstracted

On-chip Memories

Off-chip

Memory](https://image.slidesharecdn.com/fpgax5-pycoram-140310083025-phpapp02/85/PyCoRAM-Python-Verilog-FPGA-IP-FPGAX-05-10-320.jpg)

![PyCoRAM [Takamaeda+,CARL’13]

n ベンダーEDK向けのPythonベースのCoRAM実装

l 計算カーネルのRTL記述とメモリアクセスパターンの

Python記述からAXI4 IPコアを自動合成

l 出来上がったIPコアをEDKでポチポチつなげばシステム完成!

n 特徴

l Pythonでのコントロールスレッド記述

• Pythonで簡単にメモリアクセスパターンを記述できる

– 独自の高位合成コンパイラでPython記述からVerilog HDLのRTLを合成

l AMBA AXI4インターコネクトのサポート

• Xilinx Platform Studio (XPS)などを用いたIPコアベースの開発を支援

l 計算ロジックの複雑なデザインに対応

• ハードウェアデザイン解析・生成のための

オープンソースツールキットPyverilogを活用

2014-03-10 @shtaxxx 14](https://image.slidesharecdn.com/fpgax5-pycoram-140310083025-phpapp02/85/PyCoRAM-Python-Verilog-FPGA-IP-FPGAX-05-14-320.jpg)

![オリジナルのCoRAMとの比較

CoRAM PyCoRAM

Language

for Control-Thread

C Python

Supported

Memory Operations

(Blocking/Non-Blocking)

Read/Write

(Blocking/Non-Blocking)

Read/Write

On-chip Interconnect CONNECT NoC [FPGA’12] AMBA AXI4

FSM Granularity

in Control Thread

LLVM-IR Python AST Node

Generate Statement

Support for User logics

No Yes

Supported FPGAs

Xilinx ML605

Altera Terasic DE-4

Any FPGAs

supporting AXI Bus

# Lines of Code

11,682 lines

(w/o CONNECT)

4,947 lines

(w/o Pyverilog)

2014-03-10 @shtaxxx 15

FSM: Finite State Machine

LLVM-IR: Low Level Virtual Machine Intermediate Representation

AST: Abstract Syntax Tree](https://image.slidesharecdn.com/fpgax5-pycoram-140310083025-phpapp02/85/PyCoRAM-Python-Verilog-FPGA-IP-FPGAX-05-15-320.jpg)

![評価用アプリケーション

n Array-sum: 配列の和を求める

l 2つのCoRAMメモリをダブルバッファで利用

l SIMD幅 (=同時に計算する要素数) を変化させてその影響を観測

• 4, 8, 16, 32, 64 (bytes)

2014-03-10 @shtaxxx 43

s3

+

s2

+

s1

+

s0

+

MUX

D[0]D[1]D[2]D[3]D[0]D[1]D[2]D[3]

sum

+

MUX

D[3] D[2] D[1] D[0]

Output

CoRAM

Memory

0

CoRAM

Memory

1

from DMA Controller 0 from DMA Controller 1](https://image.slidesharecdn.com/fpgax5-pycoram-140310083025-phpapp02/85/PyCoRAM-Python-Verilog-FPGA-IP-FPGAX-05-43-320.jpg)

![結果:メモリバンド幅利用率

n 結構良い感じでメモリバンド幅を使えている

l Atlys: 85.5% (@ 16-byte)

l ML605: 84.9% (@ 64-byte)

n 100%使い切れていない理由

l 各DMACのトランザクションがシーケンシャルになっているから

• 結果,メモリアクセスレイテンシが性能にダイレクトに影響

2014-03-10 @shtaxxx 44

0

0.2

0.4

0.6

0.8

1

4 8 16 32 64

BandwidthUtilization

SIMD size [byte]

0

0.2

0.4

0.6

0.8

1

4 8 16 32

BandwidthUtilization

SIMD size [byte]

Atlys (Spartan-6) ML605 (Virtex-6)](https://image.slidesharecdn.com/fpgax5-pycoram-140310083025-phpapp02/85/PyCoRAM-Python-Verilog-FPGA-IP-FPGAX-05-44-320.jpg)

![性能

n 全実行時間から転送時間を引いた正味の計算時間を比較

n リファレンスデザインと比較して大幅な速度向上

l 6段MIPSコアのみの構成で平均3.5倍の高速化

l 6段MIPSコア+アクセラレータ2種の構成で

平均13.2倍,最大47.1倍(ステンシル計算)の高速化

2014-03-10 @shtaxxx 53

3.9

1.4

5.9 4.7 3.53.9

35.2

47.1

4.7

13.2

0

5

10

15

20

25

30

35

40

45

50

310_sort 320_mm 330_stencil 340_spath Gmean

RelativePerformance

6-stage

6-stage+ACC

14.2 14.2

16.0

20.8

3.6

9.8

2.7

4.4

3.6

0.4 0.3

4.4

0

5

10

15

20

25

310_sort 320_mm 330_stencil 340_spath

Time[sec]

Ref

6-stage

6-stage+ACC](https://image.slidesharecdn.com/fpgax5-pycoram-140310083025-phpapp02/85/PyCoRAM-Python-Verilog-FPGA-IP-FPGAX-05-53-320.jpg)