Lec Jan22 2009

0 likes731 views

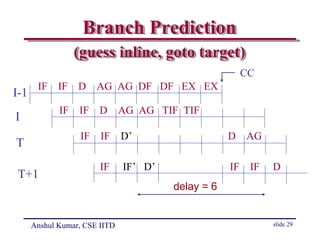

The document discusses techniques for improving branch performance in pipelined processors, including branch elimination, branch speed up, branch prediction, and branch target capture. Branch speed up techniques aim to reduce the time required to compute condition codes and determine the branch outcome. These include early target address generation, increasing the gap between condition checking and branching by inserting noped instructions, and delayed branching. Branch prediction involves guessing the branch outcome and speculatively executing down that path to reduce delays if the prediction is correct. Static prediction strategies make predictions based on the instruction type and known branch probabilities.

1 of 62

Downloaded 49 times

More Related Content

More from Ravi Soni (8)

Ad