TWISummit 2019 - Return of Reconfigurable Computing

- 2. Engineering for Research Hypotheses 1. Scientific computing is facing challenges, at par those faced by the Internet giants. 1. Enterprise computing has frameworks and tools to benefit scientific computing. Vision To build a community, working exclusively with research organisations for building tools for scientific exploration, that will enable us to discover patterns, frameworks, and computer-science of the third horizon H1: Business-as- usual (known known) H2: Known challenges (Known unknown) H3: New frontiers (Unknown unknown) ©ThoughtWorks 2019

- 3. Three formidable trends Courtesy: 1. https://en.wikipedia.org/wiki/File:Cloudburst_on_phoenix.jpg 2. https://en.wikipedia.org/wiki/Attractor#/media/File:Lorenz_attractor_yb.svg 3. https://www.publicdomainpictures.net/en/view-image.php?image=251903&picture=moores-law-installation The Data Deluge Fading of the Moore’s LawComplexity ©ThoughtWorks 2019

- 4. Moore’s Law The observation that the number of transistors in a dense integrated circuit doubles about every two years.2 1.Image: https://www.publicdomainpictures.net/en/view-image.php?image=251903&picture=moores-law-installation 2. https://en.wikipedia.org/wiki/Moore%27s_law ©ThoughtWorks 2019

- 5. Moore’s Law In Action Time First Teraflop Supercomputer (Intels ASCI RED) 1997 2007 ?? 20272017 FIrst Teraflop Chip (Intel MIC) ©ThoughtWorks 2019

- 6. Fading of Moore’s Law Source: Hennessy, J.L. and Patterson, D.A., 2019. A new golden age for computer architecture. Communications of the ACM, 62(2), pp.48-60. ©ThoughtWorks 2019

- 7. Extracting every bit of performance Source: Hennessy, J.L. and Patterson, D.A., 2019. A new golden age for computer architecture. Communications of the ACM, 62(2), pp.48-60. ©ThoughtWorks 2019

- 8. Towards ‘A New Golden Age For Computer Architecture’ General Purpose Computing Special Purpose Computing Dr. David A. Patterson Dr. John L. Hennessy Turing Laureates 2017 Source: Hennessy, J.L. and Patterson, D.A., 2019. A new golden age for computer architecture. Communications of the ACM, 62(2), pp.48-60. ©ThoughtWorks 2019

- 9. Architectural Vision of Dr. Patterson & Dr. Hennessy Domain Specific Architectures (Accelerators) 1010 + - * / 1010 OS + Frameworks Domain Specific Languages Agile GPUs DSPs ASICs ©ThoughtWorks 2019

- 10. Domain-specific architectures & languages Domain-specific language: A computer language specialized to a particular application domain. ● SQL (Database) ● HTML (Webpages) ● MATLAB (Matrix operations) ● TensorFlow (Machine Learning) Domain-specific architecture: A class of processors tailored for a specific domain—programmable and often Turing-complete but tailored to a specific class of applications. ● Graphics Processing Unit (Image & Video processing) ● Tensor Processing Unit (Machine Learning) ● ROACH (Radio Astronomy) Source: Hennessy, J.L. and Patterson, D.A., 2019. A new golden age for computer architecture. Communications of the ACM, 62(2), pp.48-60. ©ThoughtWorks 2019

- 11. Host-Accelerator Model CPU (Host) Accelerator Commands Data Bus (PCI, AGP, etc.) ©ThoughtWorks 2019

- 12. Architecture Spectrum General Purpose Architecture Application Specific Architecture Reconfigurable Architecture GPU Performance Ease of development ©ThoughtWorks 2019

- 13. Field Programmable Gate Array (FPGA) Field Programmable: Can be programmed on field (Reconfigurable) Gate Array: Array of logic gates/blocks 1. https://commons.wikimedia.org/wiki/File:Helicopter-PicooZ.jpg 2. https://commons.wikimedia.org/wiki/File:Lego_blocks.jpg 3. https://commons.m.wikimedia.org/wiki/File:LEGO_City_10159_LEGO_City_Airport_(41080418800).jpg ©ThoughtWorks 2019

- 14. ASIC FPGA ● Non-reconfigurable ● High development cost ● High cost for bug fixing ● High performance for given application ● High operating frequency ● Suitable for mass production ● Reconfigurable ● Low development cost ● No or low cost for bug fixing ● Performance is less compared to ASIC ● Limited operating frequency ● Suitable for few quantities ©ThoughtWorks 2019

- 15. More about FPGA ● Inherent Parallelization ● No processor → reduced overhead of instructions ● Low power consumption ● Programming paradigm different from other software languages ● Number of logic blocks implies size of FPGA (an important parameter for selection) ● Algorithm in the form of digital circuit ©ThoughtWorks 2019

- 16. Why Now? ● FPGAs are not just simple programmable logic devices anymore ● High end state-of-the-art FPGAs ● Evolving ecosystem around FPGA ● Increasing need for reconfigurable computing ● Traditionally → Static Reconfiguration Now → Dynamic & Partial Reconfiguration 2000 2018 ~ 15k Logic Elements ~ 1m Logic Elements Full applicationSimple logic in embedded systems ©ThoughtWorks 2019

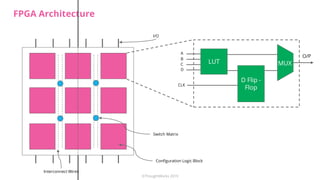

- 17. FPGA Architecture LUT D Flip - Flop MUX O/P A B C D CLK Interconnect Wires Configuration Logic Block Switch Matrix I/O ©ThoughtWorks 2019

- 18. Mapping to programming constructs if… else… Ternary Operator Memory cell Maintain State Static mapping Mux D Flip Flop LUT CLK D Q Q’ O/P I0 I1 SEL A B C D O/P ©ThoughtWorks 2019

- 19. Hardware Description Languages ● VHDL ● Verilog ● SystemVerilog ● MyHDL (HLS) ● CHISEL (HLS) Computer languages specialized to describe behavior of electronic (mostly digital) circuits. CLK Q Q’ D CLK Q Q’ D CLK Q Q’ D CLK Q Q’ Dio_in r0 r1 r2 r3 Shift Register io_out ©ThoughtWorks 2019

- 20. CHISEL (Constructing Hardware In Scala Embedded Language) ● Scala-based DSL ● Open source ● Testing (PeekPokeTester) ● Interoperability with Verilog ● Better positioned for Agile Development ©ThoughtWorks 2019

- 21. Evolving Ecosystem ● Libraries/tools/IPs: ○ Mostly used components available in the form of IP cores which can be directly used in your design ○ High level synthesis languages can have more number of open IP cores ○ Even microprocessor specifications such as RISC V available as open source ● Adoptions: Amazon cloud/Microsoft Azure/Intel/Apple ● Heterogeneous computing to next level ○ Traditionally, heterogeneity → CPU + (fixed) Accelerator ○ Now, heterogeneity → CPU + (reconfigurable) Accelerator ©ThoughtWorks 2019

- 22. Collaboration with TIFR-National Centre for Radio Astrophysics ● Home of Giant Metrewave Radio Telescope (GMRT) ● Signal processing: Real-time radio frequency interference (RFI) mitigation ● Choosing right combination of accelerators for the best performance - CPU, GPU, FPGA ©ThoughtWorks 2019

- 23. Square Kilometre Array Radio Telescope ● Data rate: 5,000 PB/day in Phase 1 (100,000 PB/day in Phase 2) ● Performance required: 250 PFLOPS in Phase 1 (25000 PFLOPS in Phase 2) (Best supercomputer today = 149 PFLOPS) ● Power Consumption (Phase 1) ○ 12.7 MW for CPU+GPU (estimated for future) ○ 3.06 MW with CPU+FPGA (estimated for future) ● http://ska-sdp.org/sites/default/files/attachments/alexander_sdp_industryapril2017_detail.pptx ● https://www.astron.nl/~broekema/papers/SDP-PDR/PDR02-01-01%20Compute%20Platform%20Hardware%20alternatives.pdf ● https://www.top500.org/lists/2019/06/ ©ThoughtWorks 2019

- 25. Implications ● Evolution of full-stack development ● Evolution of devops ● Open source hardware development ● Upgradable hardware especially microprocessors ● Reconfigurable provisioning in cloud computing ©ThoughtWorks 2019

- 26. Evolution of Full Stack Development UI/UX Middleware Business Logic Database Dev Ops Cloud Platform Reconfigurable DSA Domain Specific Language UI/UX Middleware Business Logic Database Dev Ops Cloud Platform UI/UX Middleware Business Logic Database ©ThoughtWorks 2019

- 27. Summary ● Fading of Moore’s law giving rise to a new golden age of computer architecture ● General purpose to special purpose computing ● Need for DSL + DSA ● FPGA as a reconfigurable architecture ● Evolution of full stack development because of DSLs & DSAs ● ThoughtWorks imagining a transformation and development practice around accelerated computing in general THANK YOU ! Please share your feedback with harshalh@thoughtworks.com bhimsenp@thoughtworks.com #TWISummit ©ThoughtWorks 2019