Digital circuits, including digital computers, are formed from binary circuits

- 1. The ARM ARCHIECTURE • The ARM processor is a Reduced Instruction Set Computer. • The ARM was originally developed at ACORN computers Ltd of Cambridge between 1983 – 1985 & ARM stood for Acorn RISC Machines • It was the first RISC Microprocessor developed for commercial use and has some significant differences from subsequent RISC architectures. • In 1990, Advanced RISC Machines Ltd was established as separate company specifically to widen the exploitation of ARM technology. 20/08/24 MC 2

- 2. ARCHITECTURAL INHERITANCE • RISC Architectures before ARM -Berkeley RISC I, Berkeley RISC II and Stanford MIPS (Microprocessor without Interlocking Pipeline Stages) Features Used by ARM: • Load Store Architecture • Fixed length 32-bit instructions • 3-address instruction formats.(Rn,Rm,Rd) (Rn,Rm source registers and Rd- destination registers) 20/08/24 MC 3

- 3. DATA SIZE AND INSTRUCTION SET 20/08/24 MC 4

- 4. REGISTERS IN ARM 20/08/24 MC 5

- 5. Current visible registers 20/08/24 OBE 6

- 6. Special purpose registers 20/08/24 OBE 7 THREE SPECIAL FUNCTION REGISTERS: • Stack pointer. • Link Register. • Program counter. • STACK POINTER (R13): It is used to store the head of the stack in the current processor mode. • LINK REGISTER(R14): It is used when the interrupt is used in program. • It is used to return when subroutine calls occurred. • PROGRAM COUNTER(R15): It is used to store the address of next instruction to be execute.

- 7. THE ARM PROGRAMMER’S MODEL 20/08/24 MC 8

- 9. THE ARM PROGRAMMER’S MODEL 20/08/24 MC 11

- 10. BANKED REGISTERS • Shows all 37 registers in the register files • 20 registers are hidden from a program at different times. These registers are called banked registers and are identified by shading the diagram. • Available only when the processor is in particular mode. Ex: abort mode has banked registers r13_abt, r14_abt and spsr_sbt 20/08/24 OBE 12

- 11. THE ARM PROGRAMMER’S MODEL The Memory System: •Data items may be 8-bit bytes, 16-bit half words or 32-bit words. Words are always aligned on 4-byte boundaries. •The ARM can be set up to access its data in either little or big endian format. Little endian: •Least significant byte of a word is stored in bits 0 7 of an addressed word. ‐ Big endian: •Least significant byte of a word is stored in bits 24 31 of an addressed word. ‐ 20/08/24 MC 14

- 12. THE ARM PROGRAMMER’S MODEL Load-Store Architecture: •ARM employs a load-store architecture. This means that the instruction set will only process (add, subtract, and so on) values which are in registers (or specified directly within the instruction itself), and will always place the results of such processing into a register. •The only operations which apply to memory state are ones which copy memory values into registers (load instructions) or copy register values into memory (store instructions). 20/08/24 MC 16

- 13. ARM Pipelining • A Pipelining is the mechanism used by RISC(Reduced instruction set computer) processors to execute instructions, • by speeding up the execution by fetching the instruction, while other instructions are being decoded and executed simultaneously. • Which in turn allows the memory system and processor to work continuously. • The pipeline design for each ARM family is different. 20/08/24 OBE 17

- 14. • Pipelining is a design technique or a process which plays an important role in increasing the efficiency of data processing in the processor of a computer and microcontroller. By keeping the processor in a continuous process of fetching, decoding and executing called (F&E cycle). 20/08/24 OBE 18

- 15. 3-stage pipeline ARM organization The register bank, which stores the processor state. Barrel Shifter, which can shift or rotate one operand by any number of bits. ALU, performs the arithmetic and logic functions required by the instruction set.

- 16. ARM Single-Cycle Instruction 3 stage piepline 20/08/24 MC 21 ARM processors up to the ARM7 employ a simple 3-stage pipeline with the following pipeline stages 1.Fetch 2.Decode 3.Execute

- 17. ARM single-cycle instruction 3-stage pipeline operation 1. When the processor is executing simple data processing instructions the pipeline enables one instruction to be completed every clock cycle. 2. An individual instruction takes three clock cycles to complete, so it has three-cycle latency, but the throughput is one instruction per cycle.

- 18. 5-Stage Pipeline ARM Organization Basic five-stage pipeline in a RISC machine (IF = Instruction Fetch, ID = Instruction Decode, EX = Execute, MEM = Memory access, WB = Register write back). The vertical axis is successive instructions; the horizontal axis is time. So in the green column, the earliest instruction is in WB stage, and the latest instruction is undergoing instruction fetch.

- 20. 5-Stage Pipeline Organization (2/2)

- 21. ARM PROCESSOR CORES • ARM Processor Core is the engine within a system that fetches ARM instructions from memory and executes them. • The ARM cores are very small, typically occupying just a few square millimeters of chip area. • Modern VLSI technology allows a large number of additional system components to be incorporated on the same chip.(like cache memory, MMU , signal processing hardware, debugging tools….etc) • The correct choice of processor core is one of the most critical decisions in the specification of a new system.

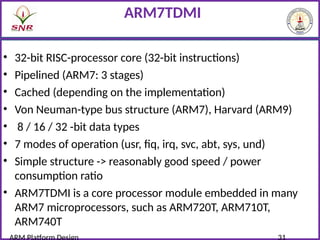

- 22. ARM7TDMI • The origins of the name are as follows: The ARM7, a 3 volt compatible rework of the ARM6 32-bit integer core, with: the Thumb 16-bit compressed instruction set; on-chip Debug support, enabling the processor to halt in response to a debug request; an enhanced Multiplier, with higher performance than its predecessors and yielding a full 64-bit result; and Embedded lCE hardware to give on-chip breakpoint and watchpoint support.

- 23. ARM7TDMI • 32-bit RISC-processor core (32-bit instructions) • Pipelined (ARM7: 3 stages) • Cached (depending on the implementation) • Von Neuman-type bus structure (ARM7), Harvard (ARM9) • 8 / 16 / 32 -bit data types • 7 modes of operation (usr, fiq, irq, svc, abt, sys, und) • Simple structure -> reasonably good speed / power consumption ratio • ARM7TDMI is a core processor module embedded in many ARM7 microprocessors, such as ARM720T, ARM710T, ARM740T

- 28. ARM TOOLS

Editor's Notes

- #23: When a multi-cycle instruction is executed the flow is less regular, as illustrated in Figure. This shows a sequence of single-cycle ADD instructions with a data store instruction, STR, occurring after the first ADD. The cycles that access main memory are shown with light shading so it can be seen that memory is used in every cycle. The datapath is likewise used in every cycle, being involved in all the execute cycles, the address calculation and the data transfer. The decode logic is always generating the control signals for the datapath to use in the next cycle, so in addition to the explicit decode cycles it is also generating the control for the data transfer during the address calculation cycle of the STR.