Hart protocol physical and data link layer implementation project

- 1. HART Protocol Physical and Data link layer Implementation Guided by Dr. C.B.Bhatt

- 2. HART - Principle HART (Highway Addressable Remote Transducer) was developed by Fisher- Rosemount to retrofit 4-to-20mA current loop transducers with digital data communication.

- 3. HART - Principle HART modulates the 4-20mA current with a low-level frequency-shift-keyed (FSK) sine-wave signal, without affecting the average analogue signal. HART uses low frequencies (1200Hz and 2200 Hz) to deal with poor cabling, its rate is 1200 Bd - but sufficient. At a basic level, most smart instruments provide core functions such as: • Control of range/zero/span adjustments • Diagnostics to verify functionality • Memory to store configuration and status information

- 4. Average current change during communication = 0 The HART protocol can be used in three ways: • In conjunction with the 4–20 mA current signal in point- to-point mode • In conjunction with other field devices in multidrop mode • In point-to-point mode with only one field device broadcasting in burst mode

- 5. HART Format The HART protocol has two formats for digital transmission of data: Poll/response mode Burst (or broadcast) mode

- 6. In the poll/response mode the master polls each of the smart devices on the highway and requests the relevant information. In burst mode the field device continuously transmits process data without the need for the host to send request messages. Although this mode is fairly fast (up to 3.7 times/second), it cannot be used in multidrop networks.

- 7. HART PROTOCOL PHYSICAL LAYER The physical layer of the HART protocol is based on two methods of communication. Analog 4–20 mA Digital frequency shift keying (FSK)

- 8. FREQUENCY SHIFT KEYING (FSK) The HART Communication Protocol is based on the Bell 202 telephone communication standard and operates using the frequency shift keying (FSK) principle. The digital signal is made up of two frequencies — 1,200 Hz and 2,200 Hz representing bits 1 and 0, respectively. Sine waves of these two frequencies are superimposed on the direct current (dc) analog signal cables to provide simultaneous analog and digital communications (Fig 1). Because the average value of the FSK signal is always zero, the 4‐20mA analog signal is not affected.

- 9. FREQUENCY SHIFT KEYING (FSK)

- 10. HART PROTOCOL DATA LINK LAYER HART data link frame format

- 11. Two-dimensional error checking, including vertical and longitudinal parity checks, is implemented in each frame. Each character or frame of information has the following parameters: 1 start bit 8 data bits 1 odd parity bit 1 stop bit

- 12. HART NETWORK Point to Point Multidrop

- 13. POINT‐TO‐POINT In point‐to‐point mode, the 4‐20mA signal is used to communicate one process variable, while additional process variables, configuration parameters, and other device data are transferred digitally using the HART Protocol. The 4‐20mA analog signal is not affected by the HART signal and can be used for control. The HART communication digital signal gives access to secondary variables and other data that can be used for operations, commissioning, maintenance and diagnostic purposes.

- 14. POINT TO POINT

- 15. BLOCK DIAGRAM OF PROJECT

- 16. HART MODEM General Description The DS8500 is a single-chip modem with Highway Addressable Remote Transducer (HART) capabilities and satisfies the HART physical layer requirements. The device integrates the modulation and demodulation of the 1200Hz/2200Hz FSK signal, has very low power consumption, and needs only a few external components due to the integrated digital signal processing. The input signal is sampled by an analog-to-digital converter (ADC), followed by a digital filter/demodulator.

- 17. HART MODEM This architecture ensures reliable signal detection in noisy environments. The output digital-to-analog converter (DAC) generates a sine wave and provides a clean signal with phase-continuous switching between 1200Hz and 2200Hz. Low power is achieved by disabling the receive circuits during transmit and vice versa. The DS8500 is ideal for low-power process control transmitters.

- 18. Applications 4–20mA Loop-Powered Transmitters for Temperature, Pressure, Flow, and Level Measurement HART Multiplexers HART Modem Interface Connectivity

- 19. Features Single-Chip, Half-Duplex, 1200bps FSK Modulation and Demodulation Digital Signal Processing Provides Reliable Input Signal Detection in Noisy Conditions Sinusoidal Output Signal with Lowest Harmonic Distortion Few External Components Enable a Space-Saving Solution Standard Component 3.6864MHz Crystal Complies to HART Physical Layer Requirements 2.7V to 3.6V Operating Voltage 285μA (max) Current Consumption Space-Saving, 5mm x 5mm x 0.8mm, 20-Pin TQFN Package

- 21. Block Diagram

- 22. Functional Description The DS8500 modem chip consists of a demodulator, carrier detect, digital filter, ADC for input signal conversion, a modulator and DAC for output signal generation, and receive and transmit state machine blocks to perform the HART communication. The Block Diagram illustrates the interface between various blocks of circuitry. The input HART signal’s noise interference is attenuated by a one-pole high pass filter that is external to the chip; the attenuated signal is digitized by the ADC and filtered by the receive state machine. The transmit state machine modulates the input to the HART- compliant signal with the help of the modulator and the DAC.

- 27. Features of C8051F340 High-speed pipelined 8051-compatible microcontroller core (up to 48 MIPS) In-system, full-speed, non-intrusive debug interface (on-chip) Universal Serial Bus (USB) Function Controller with eight flexible endpoint pipes, integrated transceiver, and 1 kB FIFO RAM Supply Voltage Regulator True 10-bit 200 ksps differential / single-ended ADC with analog multiplexer On-chip Voltage Reference and Temperature Sensor On-chip Voltage Comparators (2) Precision internal calibrated 12 MHz internal oscillator and 4x clock multiplier Internal low-frequency oscillator for additional power savings

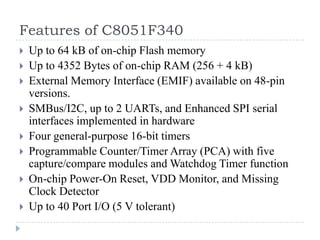

- 28. Features of C8051F340 Up to 64 kB of on-chip Flash memory Up to 4352 Bytes of on-chip RAM (256 + 4 kB) External Memory Interface (EMIF) available on 48-pin versions. SMBus/I2C, up to 2 UARTs, and Enhanced SPI serial interfaces implemented in hardware Four general-purpose 16-bit timers Programmable Counter/Timer Array (PCA) with five capture/compare modules and Watchdog Timer function On-chip Power-On Reset, VDD Monitor, and Missing Clock Detector Up to 40 Port I/O (5 V tolerant)

- 29. Summary of HART benefits Simultaneous analog and digital communications Allows other analog devices on the highway Allows multiple masters to control same smart instrument Multiple smart devices on the same highway Long distance communications over telephone lines Two alternative transmission modes Flexible messaging structure for new features Up to 256 process variables in any smart field device

- 30. Thank You