advanced fpga based system design VI.ppt

- 1. 1 Advanced FPGA Based System Design Lecture-11 & 12 VHDL Finite State Machines By: Dr Imtiaz Hussain imtiaz.hussain@faculty.muet.edu.pk

- 2. 2 Contents • Finite State Machines • Design Style#1 • Design Style#2 • Signals & Variables

- 3. 3 Introduction • Several approaches can be conceived to design a FSM. • We will discuss in detail one style that is well structured and easily applicable.

- 4. 4 Design Style#1 • In this style, the design of the lower section of the state machine is completely separated from that of the upper section.

- 5. 5 Design Style#1 • It contains user-defined enumerated data type (here called state), which lists all possible states of the machine.

- 6. 6 Design Style#1 • Design of Lower (Sequential) section • The flip-flops are in the lower section, so clock and reset are connected to it. • The other lower section’s input is nx_state (next state), while pr_state (present state) is its only output. • Being the circuit of the lower (sequential) section, a PROCESS is required, in which any of the sequential statements (IF, WAIT, CASE, or LOOP, can be employed.

- 7. 7 Design Style#1 • Design of Lower (Sequential) section – A typical design template for the lower section is the following:

- 8. 8 Design Style#1 • Design of Upper (Combinational) section • The upper section is fully combinational, so its code does not need to be sequential; concurrent code can be used as well. • In the design template shown in next slide, sequential code is employed, with the CASE statement playing the central role.

- 9. 9

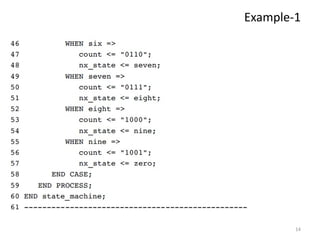

- 10. 10 Example-1 • A BCD counter is an example of Moore Machine

- 11. 11 Example-1

- 12. 12 Example-1

- 13. 13 Example-1

- 14. 14 Example-1

- 15. 15 Example#2 • The system has two states (state A and state B). • State must change from one to the other every time d = ‘1’ is received. • The desired output is x = a when the machine is in state A, or x =b when in state B. • The initial (reset) state is state A.

- 16. 16 Example#2

- 17. 17 Example#2

- 18. 18 Example#2