DHow2 - L4

- 1. Introduzione ai Sistemi Embedded DRESD How To (DHow2) - L4 POLITECNICO DI MILANO D ynamic R econfigurability in E mbedded S ystems D esign DRESD Team [email_address]

- 2. Outline Sistemi embedded Introduzione Caratteristiche Soluzioni architetturali System-on-Chip Microprocessori Memorie Interfacciamento Tecnologie programmabili Metodologia di progetto

- 3. Sistemi embedded: introduzione Sistemi dedicati a classi specifiche di applicazioni Ottimizzazione Diversificazione a livello architetturale Requisiti funzionali Vincoli: dimensioni, consumo di potenza, costo, ...

- 4. Sistemi embedded: caratteristiche Dimensioni Consumo energetico Scelta della tecnologia Interfacce di comunicazione Quantità di dati da trasferire Tipo di utilizzo Interfacce utente Volumi Time-to-market Tempo di vita

- 5. Soluzioni architetturali Printed Circuit Board (PCB) Assemblaggio di componenti discreti su una basetta di materiale plastico che realizza le interconnessioni necessarie System-on-Chip SoC Multi-Processor System-on-Chip (MPSoC) Multi-Chip Module (MCM) Network on Chip (NoC) Sistemi distribuiti Funzionalità complessa su più sottosistemi fortemente interagenti tra loro tramite reti di comunicazione Wireless Sensor Network (WSN)

- 6. Soluzioni architetturali: System-on-Chip (1/2) Architettura basata su un singolo chip in tecnologia intergrata che ospita l’intero sistema Vantaggi Prestazioni Assorbimento energetico Numero di pin di ingresso/uscita più basso Costo

- 7. Soluzioni architetturali: System-on-Chip (2/2) Componenti funzionali Microprocessori Memorie Blocchi digitali dedicati Core digitali standard: encoder, decoder, filtri, ... Blocchi di temporizzazione: timer, watchdog, ... Blocchi di alimentazione: regolatori di tensione, ... Interfacce: analogiche, seriali, parallele, di rete, ...

- 8. Microprocessori (1/2) General Purpose Processor (GPP) Architettura di calcolo per applicazioni in campi anche molto diversi Architetture CISC (Complex Instruction Set Computer): ampio instruction set costituito da istruzioni complesse Architetture RISC (Reduced Instruction Set Computer): instruction set limitato con istruzioni mediamente semplici Architetture CISC/RISC: scomposizione di istruzioni CISC in istruzioni simili alle istruzioni RISC Architetture superscalari: architetture con più di un’unità di elaborazione Architetture EPIC/VLIW (Explicitly Parallel Instruction Computer / Very Long Instruction Word): istruzioni elementari in una sola parola di grandi dimensioni

- 9. Microprocessori (2/2) Processori dedicati Architetture di microprocessore ottimizzate per applicazioni specifiche Digital Signal Processor (DSP): elaborazione numerica Network Processor (NP): applicazioni di reti (e.g. elaborazione di pacchetti) Micro Controller Unit (MCU): microprocessori che dispongono di molte periferiche e interfacce integrate su singolo chip, adatti per carico computazionale modesto e vincoli sulle risorse hardware

- 10. Memorie (1/2) Parametri caratteristici Tempo di accesso Granularità Tipo di accesso: casuale, FIFO, LIFO, ... Funzione: operazioni per cui è concepita la memoria Programmabilità: memorie volatili vs non volatili Classificazione Static Random Access Memory (SRAM) Dynamic Random Access Memory (DRAM) Read Only Memory (ROM) Electrically Programmable Read Only Memory (EPROM) Electrically Erasable Programmable Read Only Memory (E2PROM) Flash

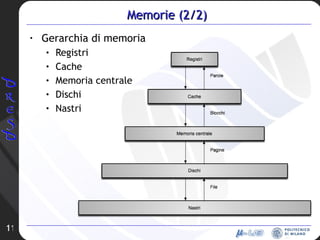

- 11. Memorie (2/2) Gerarchia di memoria Registri Cache Memoria centrale Dischi Nastri

- 12. Interfacciamento (1/2) Trasferimento di dati tra porzioni dello stesso sistema Indirizzamento Memory mapped I/O: spazio di indirizzamento del microprocessore suddiviso in sezioni assegnate ai dispositivi Standard I/O: bus di controllo con una linea aggiuntiva che indica se l’indirizzo si riferisce alla memoria o alle periferiche Port mapped I/O: comunicazione tra microprocessore e periferiche tramite linee dedicate Extended I/O: uso di un dispositivo hardware, detto Parallel I/O (PIO), che si interfaccia con il microprocessore tramite bus o porta

- 13. Interfacciamento (2/2) Polling Verifica ciclica di tutte le unità di Input/Output tramite test dei bit di stato associati ad ogni periferica Interrupt Messaggio, inviato dalla periferica al microprocessore, che indica la disponibilità di un nuovo dato da leggere Direct Memory Access (DMA) DMA controller

- 14. Tecnologie programmabili (1/2) Programmable Logic Array (PLA) Programmable Array Logic (PAL) Generic Array Logic (GAL) Complex Programmable Logic Device (CPLD)

- 15. Tecnologie programmabili (2/2) Field Programmable Gate Array (FPGA) Configurable Logic Block (CLB) Input/Output Block (IOB) Interconnessioni

- 16. Metodologia di progetto Procedura seguita per il progetto Top-down Bottom-up Modello del sistema Applicazione di tecniche di scheduling, HW/SW codesign, ... Simulazione Sintesi (HW) / compilazione (SW) Implementazione fisica

![Introduzione ai Sistemi Embedded DRESD How To (DHow2) - L4 POLITECNICO DI MILANO D ynamic R econfigurability in E mbedded S ystems D esign DRESD Team [email_address]](https://image.slidesharecdn.com/es-1228829981790664-9/85/DHow2-L4-1-320.jpg)