Error detection enhanced decoding of difference set codes for memory applications

- 1. 1 Error Detection Enhanced Decoding of Difference Set Codes for Memory Applications SHERIN DEENA SAM

- 2. 2 What a difference a bit makes!!! • NASA engineers believe they have traced the cause of Voyager 2's glitch (in 2010) to single flip of bit in the spacecraft’s memory. • "A value in a single memory location was changed from a 0 to a 1," said JPL’s Veronia McGregor.

- 3. 3 Contents • Error Correcting Code Memory • OSMLD Difference Set Codes (21,11) DS code • Conventional Decoder for (21,11) DS code Avoiding silent data corruption • Error Detection Majority Logic Decoding

- 4. 4 Error Correcting Code Memory

- 5. 5 ECC memory • Error correcting code memory is a type of computer data storage that can detect and correct common kinds of internal data corruption. • It is used in computers where data corruption cannot be tolerated under any circumstances, such as for scientific or financial computing, as spacecrafts and as servers. • Electrical or magnetic interference can cause a single bit to spontaneously flip to the opposite state. • Majority of soft errors in RAM chips occur as a result of ionizing radiation. • ECC is used in NAND flash, SRAM, DRAM, SDRAM etc. • ECC schemes used are BCH Error Correction Code, Euclidean Geometry ECC, Difference Set ECC.

- 6. 6 OSMLD Difference Set Codes DS codes are attractive because they are One Step Majority Logic Decodable (OSMLD).

- 7. 7 Difference Set • P={l0,l1,l2,……,lq} is a set with q+1 nonnegative integers such that 0≤lo<l1<l2<…..<lq ≤q(q+1) • q(q+1) ordered differences D={lj-li:j≠i} • P is a perfect simple difference-set of order q iff 1. All positive differences in D are distinct. 2. All negative differences in D are distinct. 3. If lj-li is a negative difference in D, then q(q+1)+1+(lj-li) is not equal to any positive difference in D. • Consider the set P= {0,2,7,8,11} with q=4 • 4.5=20 ordered differences D={2,7,8,11,5,6,9,1,4,3, -2,-7,-8,-11,-5,-6,-9,-1,-4,-3}

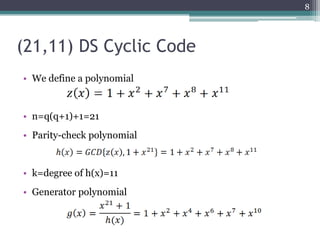

- 8. 8 (21,11) DS Cyclic Code • We define a polynomial • n=q(q+1)+1=21 • Parity-check polynomial • k=degree of h(x)=11 • Generator polynomial

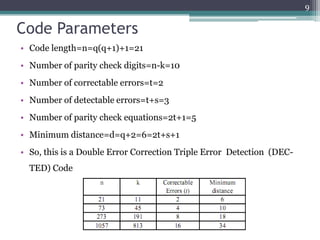

- 9. 9 Code Parameters • Code length=n=q(q+1)+1=21 • Number of parity check digits=n-k=10 • Number of correctable errors=t=2 • Number of detectable errors=t+s=3 • Number of parity check equations=2t+1=5 • Minimum distance=d=q+2=6=2t+s+1 • So, this is a Double Error Correction Triple Error Detection (DEC- TED) Code

- 10. 10 Dual Code • (n, n-k) cyclic code. • Code generated by • It gives the dual code of the code generated by g(x). • It is in the null space of the DS code generated by g(x). • We define a polynomial

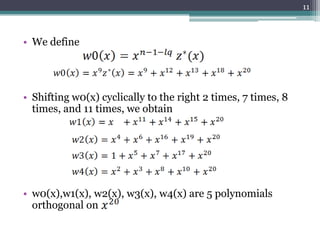

- 11. 11 • We define • Shifting w0(x) cyclically to the right 2 times, 7 times, 8 times, and 11 times, we obtain • w0(x),w1(x), w2(x), w3(x), w4(x) are 5 polynomials orthogonal on

- 12. 12 • We can form 5 parity-check sums orthogonal on e20. • A1=e9+e12+e13+ e18+e20 • A2=e1+e11+e14+e15+e20 • A3=e4+e6+e16+e19+e20 • A4=e0+e5+e7+e17+e20 • A5=e2+e3+e8+e10+e20 • e20 is checked by all 5 check sums and no other error digit is checked by more than one check sum.

- 13. 13 One Step Majority Logic Decoding • If e20 = 1 and if there is one or no error occurring among the other 20 digit positions, then at least 4 of the 5 check sums are equal to 1. • If e20= 0 and if there are two or fewer errors occurring among the other 20 digit positions, then at least 3 of the 5 check sums are equal to 0. ▫ If there are two or fewer errors , the one step majority logic decoding always results in correct decoding of e20. • Consider e9= e1= e4= 1. We have A1=1, A2=1, A3=1, A4=0,A5=0. Since the majority of the five sums is 1, e20 is decoded as 1. This results in an incorrect decoding. • Thus, by one-step majority logic decoding, the code is capable of correcting any error pattern with two or fewer errors.

- 14. 14 Conventional Decoder for (21,11) DS code

- 15. 15 Decoder for (21,11) DS code

- 16. 16 Correction of 2 errors

- 17. 17 SDC- Silent Data Corruption • Considering the (21,11) DS code, when a triple error occurs, it can cause Silent Data Corruption (SDC) because it can trigger a miscorrection that then can result in the word being decoded into another valid coded word.

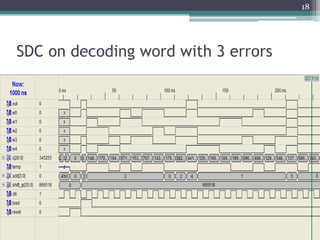

- 18. 18 SDC on decoding word with 3 errors

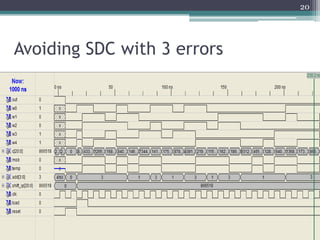

- 19. 19 Avoiding SDC • To avoid SDC, the proposed decoder for the (21,11) code is the same but requiring at least four check equations to be one to perform a bit correction. • Requiring at least t+2 ones instead of a majority of ones will ensure that there is no miscorrection with t+1 errors and at the same time guarantees that t errors are corrected.

- 20. 20 Avoiding SDC with 3 errors

- 21. 21 Issues • The decoder requires 21 iterations to decode a word. This results in a large latency that in a memory application would increase the access time. • Additionally, the number of iterations would increase linearly with the length of the coded word.

- 22. 22 Error Detection Majority Logic Decoding (EDMLD)

- 23. 23 Avoiding decoding latency • All errors affecting five or less bits are detected in the first three iterations. • This can be used to reduce the decoding latency by stopping the process when no error has been detected in the first three iterations. • This technique reduces the decoding latency significantly as most words will have no errors.

- 24. 24 No error detected in 3 cycles

- 25. 25 Error detected in 3 cycles

- 26. 26 Detection of uncorrectable errors • Additionally, it can also be used to detect uncorrected errors once the decoding has been completed. • This will be useful to detect errors that affect t+1 bits and can not be corrected.

- 29. 29 Conclusion • The decoder has been implemented in Verilog HDL. • The conventional decoder has been modified to avoid SDC. • Error Detection Majority Logic Decoding (EDMLD) has been done which provides detection of errors in addition to correction. ▫ It reduces latency. ▫ It detects errors that affect t+1 bits and can not be corrected.

- 30. 30 References [1]S. Liu, P. Reviriego and J. A. Maestro “Error-Detection Enhanced Decoding of Difference Set Codes for Memory Applications ” IEEE Trans. on Device and Materials Reliability, Vol. 12, No. 2, 2012, pp 335 – 340. [2]S. Liu, P. Reviriego and J. A. Maestro “Efficient Majority Logic Fault Detection with Difference-Set Codes for Memory Applications” IEEE Trans. on Very Large Scale Integration Systems, Vol. 20, No. 1, 2012, pp 148-156. [3]S. Lin and D. J. Costello, Error Control Coding, 2nd ed. Englewood Cliffs, NJ: Prentice-Hall, 2004.

- 31. 31 THANK YOU

![30

References

[1]S. Liu, P. Reviriego and J. A. Maestro “Error-Detection Enhanced Decoding

of Difference Set Codes for Memory Applications ” IEEE Trans. on Device

and Materials Reliability, Vol. 12, No. 2, 2012, pp 335 – 340.

[2]S. Liu, P. Reviriego and J. A. Maestro “Efficient Majority Logic Fault

Detection with Difference-Set Codes for Memory Applications” IEEE Trans.

on Very Large Scale Integration Systems, Vol. 20, No. 1, 2012, pp 148-156.

[3]S. Lin and D. J. Costello, Error Control Coding, 2nd ed. Englewood

Cliffs, NJ: Prentice-Hall, 2004.](https://image.slidesharecdn.com/errordetectionenhanceddecodingofdifferencesetcodesformemoryapplications-120927022519-phpapp01/85/Error-detection-enhanced-decoding-of-difference-set-codes-for-memory-applications-30-320.jpg)