OSVC_Meta-Data based Simulation Automation to overcome Verification Challenges of SoC Interconnect Bus Matrix.pptx

- 1. Three Essential Principles of Solution P&D 1. Actively pursue innovative activities that increase Work Efficiency. 2. Grow together through transparent information sharing and development Knowledge Sharing. 3. Quality of the solution products should be Prioritized In Any Situation. Meta-Data based Simulation Automation to Overcome Verification Challenges August 23,2020 | Soham Mondal | Girish Kumar Gupta

- 2. 1/11 Outline Challenges Test Automation Flow Case Studies and Simulation Results Benefits and Comparison with Counterpart Industry Tool Conclusion Author Profile

- 3. 2/11 Challenges Validating a huge number of masters of standard bus protocol brings in challenges in end-to-end verification of large SoC Bus Matrix Such test bench creation with vendor VIP are effort-intensive , time-consuming and inherently error prone Usage of vendor VIP has its’ own challenges and requires close communication with vendor Design versions changes with verification cycle with change in system configuration, which again requires manual modification of test bench

- 4. 3/11 Test Automation Flow • IEEE-1685 IPXACT metadata is parsed by automation scripts and meaningful design information database are created on-the-fly as maps and in csv and excel sheets etc., which serve as inputs to the tool. • Database is fed as inputs to scripts. With the click of a button, test bench/verification environment with all needed capabilities is automatically generated, validated and ready for verification. • Next user inputs compilation , elaboration and simulation design specific defines and simulator tool options in generated configuration text file. Next run a second script and with this, Makefiles and test environment files like setup tool and wave dumping tcl gets created. • User can now start verification. Thus ‘time to first test’ which is often in order of months to weeks depending on design complexity is reduced to less than an hour with proposed solution. Key Features: • Primary Capabilities Supports AMBA AXI3,AXI4,AHB Lite 5, APB etc., Uses industry-proven Cadence AMBA VIP with all included capabilities. Supports custom VIP. Complete test bench generation with all required capabilities tailored for SAMSUNG memory SoC needs. • Advanced Capabilities Connected passive agent to shadow DUT and catch protocol violations. In-built scoreboard for data-integrity checks and ID-mismatch checks. Automated termination of tests when slave DUT is not responding to sent transaction. Normal as well as extensive SAMSUNG tailored test-suites which incorporate variable burst-size, length, kind and partial strobes etc., Generation of comprehensive report matrix containing parity/user-signal error, non-responsive slaves, protocol violations, etc.,

- 5. 4/11 Testbench Components Thus a generic interconnect auto-generated testbench with Cadence bus Protocol VIPs integrated contains the following components- • Top level Testbench file • Top level Environment • Master AXI , AHB , APB agents with monitors and configuration component instantiated within them • Top level virtual sequencer containing all agent sequencer handles • Top level virtual sequences containing all the write and read sequences • Top level SVE file for configuring the VIP agent’s HDL path • SOMA directory containing all – Specification of Modelling architecture(SOMA) files and HDL instantiation modules • Base virtual sequence library • AXI and AHB top level test library containing basic and custom read-after-write tests • Make files and run scripts to simulate the Test Bench on commercial simulator

- 7. 6/11 Case Studies and Simulation Results Section AXI Bus Matrix: 32 Master and 32 Slaves AHB Bus Matrix:16 Masters and 16 Slaves Automation Manual Automation Manual Custom Standard Input format creation time(A) 2 hours (partial scripting involved) Not Applicable 1 hours (partial scripting involved) Not Applicable Verification Environment creation(B) Scripts create all these components (20 seconds approx.) 24 hours Scripts create all these components (10 seconds approx.) 12 hours Tb Top Creation(C) 24 hours 12 hours Scoreboard Creation(D) 8 hours 4 hours Test Case coding(E) 8 hours 4 hours Configuration Inputs and simulation script creation(F) 6 hours 3 hours Simulation time to attain 100% coverage(G) 72 hours 96 hours 56 hours 82 hours Verification time for 1 Cycle [A:G] 74 hours 166 hours 57 hours 117 hours Verification time for SoC Project [A:G]+[A,D:G]x3 296 hours 592 hours 228 hours 432 hours Saved Verification Time 500 hours! Results: • Tried and tested for ELAN SSD Bus Matrix Deployed Successfully in ELAN E2E verification. Verification productivity improved by more than 70% (Complete E2E verification done in 3 weeks compared to 3 months earlier) 1 document bug and 8 RTL bugs are caught immediately within 1 week of verification for just 2 iterations of RTL version. This proves the effectiveness of test-suite and capabilities of auto-generated test-bench. Future Enhancements Currently E2E Automation is deployed for SoC NOC/NIC verification. It shall be extended to SRAM SECDED E2E verification and other bus matrix verification of similar nature. Currently supports protocols like AXI, AHB, APB. Can be extended to other extensive buses.

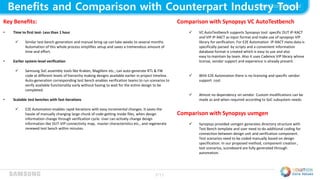

- 8. 7/11 Benefits and Comparison with Counterpart Industry Tool Key Benefits: • Time to first test- Less than 1 hour Similar test bench generation and manual bring up can take weeks to several months. Automation of this whole process simplifies setup and saves a tremendous amount of time and effort. • Earlier system-level verification Samsung SoC assembly tools like Kraken, Magillem etc., can auto-generate RTL & FW code at different levels of hierarchy making designs available earlier in project timeline. Auto-generation corresponding test bench enables verification teams to run scenarios to verify available functionality early without having to wait for the entire design to be completed. • Scalable test benches with fast iterations E2E Automation enables rapid iterations with easy incremental changes. It saves the hassle of manually changing large chunk of code getting inside files, when design information change through verification cycle. User can actively change design information like DUT-VIP connectivity map, master characteristics etc., and regenerate renewed test bench within minutes. Comparison with Synopsys VC AutoTestbench VC AutoTestbench supports Synopsys tool specific DUT IP-XACT and VIP IP-XACT as input format and make use of synopsys VIP library for verification. For E2E Automation IP-XACT meta-data is specifically parsed by scripts and a convenient information database format is created which is easy to use and also easy to maintain by team. Also it uses Cadence VIP library whose license, vendor support and experience is already present. With E2E Automation there is no licensing and specific vendor support cost. Almost no dependency on vendor. Custom modifications can be made as and when required according to SoC subsystem needs. Comparison with Synopsys uvmgen Synopsys provided uvmgen generates directory structure with Test Bench template and user need to do additional coding for connection between design unit and verification component. Test scenarios need to be coded manually based on design specification. In our proposed method, component creation , test scenarios, scoreboard are fully generated through automation.

- 9. 8/11 Conclusion • Through this approach, verification cycle time is reduced by a significant percentage and major dependencies on domain specific bus protocol knowledge and human errors are eliminated. • Proposed method is deployed, tried and tested with a set of bus matrix developed for Samsung memory controller SoC products. • Thus, E2E Automation enables a systematic, thorough, scalable approach to SoC-level interconnect verification by simplifying and automating the time-consuming and error-prone process of test bench generation.

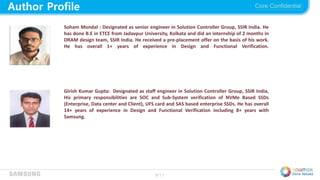

- 10. 9/11 Author Profile Soham Mondal : Designated as senior engineer in Solution Controller Group, SSIR India. He has done B.E in ETCE from Jadavpur University, Kolkata and did an internship of 2 months in DRAM design team, SSIR India. He received a pre-placement offer on the basis of his work. He has overall 1+ years of experience in Design and Functional Verification. Girish Kumar Gupta: Designated as staff engineer in Solution Controller Group, SSIR India, His primary responsibilities are SOC and Sub-System verification of NVMe Based SSDs (Enterprise, Data center and Client), UFS card and SAS based enterprise SSDs. He has overall 14+ years of experience in Design and Functional Verification including 8+ years with Samsung.

- 11. Thank You Speciality Ownership Leadership Upgrowth Together Integrity Openness Now S O L U T I O N C O R E V A L U E S

![6/11

Case Studies and Simulation Results

Section

AXI Bus Matrix:

32 Master and 32 Slaves

AHB Bus Matrix:16 Masters and 16

Slaves

Automation Manual Automation Manual

Custom Standard Input format

creation time(A)

2 hours

(partial scripting involved)

Not Applicable 1 hours

(partial scripting

involved)

Not Applicable

Verification Environment creation(B)

Scripts create all these

components

(20 seconds approx.)

24 hours

Scripts create all

these components

(10 seconds approx.)

12 hours

Tb Top Creation(C) 24 hours 12 hours

Scoreboard Creation(D) 8 hours 4 hours

Test Case coding(E) 8 hours 4 hours

Configuration Inputs and simulation

script creation(F)

6 hours 3 hours

Simulation time to attain 100%

coverage(G)

72 hours 96 hours 56 hours 82 hours

Verification time for 1 Cycle [A:G] 74 hours 166 hours 57 hours 117 hours

Verification time for SoC Project

[A:G]+[A,D:G]x3

296 hours 592 hours 228 hours 432 hours

Saved Verification Time 500 hours!

Results:

• Tried and tested for ELAN SSD Bus Matrix

Deployed Successfully in ELAN E2E

verification. Verification productivity

improved by more than 70% (Complete E2E

verification done in 3 weeks compared to 3

months earlier)

1 document bug and 8 RTL bugs are caught

immediately within 1 week of verification

for just 2 iterations of RTL version. This proves the

effectiveness of test-suite and capabilities of

auto-generated test-bench.

Future Enhancements

Currently E2E Automation is deployed for SoC

NOC/NIC verification. It shall be extended to

SRAM SECDED E2E verification and other bus

matrix verification of similar nature.

Currently supports protocols like AXI, AHB, APB.

Can be extended to other extensive buses.](https://image.slidesharecdn.com/osvcmeta-databasedsimulationautomationtoovercomeverificationchallengesofsocinterconnectbusmatrix-240426082511-867022d7/85/OSVC_Meta-Data-based-Simulation-Automation-to-overcome-Verification-Challenges-of-SoC-Interconnect-Bus-Matrix-pptx-7-320.jpg)