SICP勉強会について

- 3. SICP MIT Structure and Interpretation of Computer Programs ( : ) Scheme

- 4. SCHEME LISP 1998 `R5RS` 50 (Gauche, Racket, etc.) Gauche

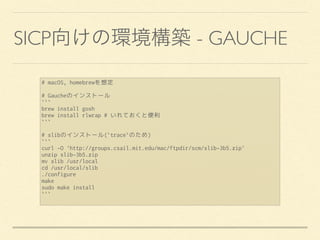

- 5. SICP - GAUCHE # macOS, homebrewを想定 # Gaucheのインストール ``` brew install gosh brew install rlwrap # いれておくと便利 ``` # slibのインストール(`trace`のため) ``` curl -O 'http://groups.csail.mit.edu/mac/ftpdir/scm/slib-3b5.zip' unzip slib-3b5.zip mv slib /usr/local cd /usr/local/slib ./configure make sudo make install ```

- 6. SCHEME HELLO WORLD $ echo '(print "Hello World!")' | gosh Hello World!

- 7. SICP -VIM vim `:!gosh %` `NeoBundle 'thinca/vim-quickrun'` `silent! map <Space>q <Plug>(quickrun)` - <Space>q `NeoBundle 'tpope/vim-surround'` S `NeoBundle ‘vim-scripts/vim-niji'` `NeoBundle 'haruyama/vim-matchopen'`

- 8. TRACE : ; fib.scm (use slib) (require 'trace) (define (fib n) (cond ((= n 0) 0) ((= n 1) 1) (else (+ (fib (- n 1)) (fib (- n 2)))))) (trace fib) (fib 3) ; CALL fib 3 ; CALL fib 2 ; CALL fib 1 ; RETN fib 1 ; CALL fib 0 ; RETN fib 0 ; RETN fib 1 ; CALL fib 1 ; RETN fib 1 ; RETN fib 2

- 11. 3 http://labs.timedia.co.jp/2014/11/reading-sicp-3.22-3.23.html Exersise 3.22 Exersise 3.55 ( )

- 13. SICP (lambda ) LISP ( ) SICP

- 14. 1 LISP(Scheme) lambda 2 ( Huffman etc) 3 . 3.4.4 ← 4 - Scheme Scheme 5 - Scheme

- 16. output = !(A) output = A || B output = A && B

- 17. . (HALF-ADDER) 2 (A B) S: (sum) C: (carry) (D E: )

- 18. . (HALF-ADDER) A B S C 0 0 0 0 1 0 1 0 0 1 1 0 1 1 0 1

- 19. (define a (make-wire)) (define b (make-wire)) (define c (make-wire)) (define d (make-wire)) (define e (make-wire)) (define s (make-wire)) (or-gate a b d) (and-gate a b c) (inverter c e) (and-gate d e s) . (HALF-ADDER)

- 20. (define (half-adder a b s c) (let ((d (make-wire)) (e (make-wire))) (or-gate a b d) (and-gate a b c) (inverter c e) (and-gate d e s) 'ok)) . ( )

- 22. : (FULL-ADDER) A B CI S CO 0 0 0 0 0 1 0 0 1 0 0 1 0 1 0 1 1 0 0 1 0 0 1 1 0 1 0 1 0 1 0 1 1 0 1 1 1 1 1 1

- 23. (define (full-adder a b c-in sum c-out) (let ((s (make-wire)) (c1 (make-wire)) (c2 (make-wire))) (half-adder b c-in s c1) (half-adder a s sum c2) (or-gate c1 c2 c-out) 'ok)) : (FULL-ADDER)

- 24. (get-signal ⟨wire⟩) (set-signal! ⟨wire⟩ ⟨new value⟩) (add-action! ⟨wire⟩ ⟨ ⟩) . (after-delay ⟨ ⟩ ⟨ ⟩) add-action!

- 25. (define (inverter input output) (define (invert-input) (let ((new-value (logical-not (get-signal input)))) (after-delay inverter-delay ;遅延時間(定数) (lambda () (set-signal! output new-value))))) (add-action! input invert-input) 'ok) - (define (logical-not s) (cond ((= s 0) 1) ((= s 1) 0) (else (error "Invalid signal" s))))

- 26. (define (and-gate a1 a2 output) (define (and-action-procedure) (let ((new-value (logical-and (get-signal a1) (get-signal a2)))) (after-delay and-gate-delay ;遅延時間(定数) (lambda () (set-signal! output new-value))))) (add-action! a1 and-action-procedure) (add-action! a2 and-action-procedure) 'ok) - (define (logical-and s1 s2) (cond ((and (= s1 0) (= s2 0)) 0) ((and (= s1 0) (= s2 1)) 0) ((and (= s1 1) (= s2 0)) 0) ((and (= s1 1) (= s2 1)) 1) (else (error "Invalid signal" s1 s2))))

- 27. 3.28 “ . or-gate , and-gate . ”

- 28. 3.28 “ . or-gate , and-gate . ” (define (or-gate a1 a2 output) (define (or-action-procedure) (let ((new-value (logical-or (get-signal a1) (get-signal a2)))) (after-delay or-gate-delay (lambda () (set-signal! output new-value))))) (add-action! a1 or-action-procedure) (add-action! a2 or-action-procedure) 'ok) (define (logical-or s1 s2) (cond ((and (= s1 0) (= s2 0)) 0) ((and (= s1 0) (= s2 1)) 1) ((and (= s1 1) (= s2 0)) 1) ((and (= s1 1) (= s2 1)) 1) (else (error "Invalid signal" s1 s2))))

- 29. 3.29 ( ) “ , , . or-gate . and-gate-delay inverter-delay .”

- 30. 3.29 ( ) “ , , . or-gate . and-gate-delay inverter-delay .”

- 31. 3.29 ( ) “ , , . or-gate . and-gate-delay inverter-delay .” A1 A2 A1 && A2 !A1 && !A2 !(!A1 && !A2) 0 0 0 1 0 1 0 0 0 1 0 1 0 0 1 1 1 1 0 1

- 32. 3.29 ( ) “ , , . or-gate . and-gate-delay inverter-delay .” (define (or-gate a1 a2 output) (let ((i1 (make-wire)) (i2 (make-wire)) (a (make-wire))) (inverter a1 i1) (inverter a2 i2) (and-gate i1 i2 a) (inverter a output)) 'ok)

- 33. 3.29 ( ) “ , , . or-gate . and-gate-delay inverter-delay .” (define (or-gate a1 a2 output) (let ((i1 (make-wire)) (i2 (make-wire)) (a (make-wire))) (inverter a1 i1) (inverter a2 i2) (and-gate i1 i2 a) (inverter a output)) 'ok) : 2 * inverter-delay + and-gate-delay

- 34. 3.30 “ 3.27 n (ripple-carry adder) . n . A1,A2, A3, ...,An B1, B2, B3, ..., Bn ( Ak Bk 0 1). n S1, S2, S3, ..., Sn , C . ripple-carry-adder . n --- Ak, Bk Sk--- , C . , . n , , , . ”

- 36. 3.30 (RIPPLE-CARRY ADDER) “ 3.27 n (ripple-carry adder) . n . A1,A2,A3, ...,An B1, B2, B3, ..., Bn ( Ak Bk 0 1). n S1, S2, S3, ..., Sn , C . ripple-carry-adder . n --- Ak, Bk Sk--- , C . ”

- 37. 3.30 (RIPPLE-CARRY ADDER) (define (ripple-carry-adder as bs ss c) (define (iter as bs ss ck-1) (if (not (null? as)) (let ((ak (car as)) (bk (car bs)) (sk (car ss)) (ck (make-wire))) (full-adder ak bk ck sk ck-1) (iter (cdr as) (cdr bs) (cdr ss) ck)))) (let ((c1 (make-wire))) (full-adder (car as) (car bs) c1 (car ss) c) (iter (cdr as) (cdr bs) (cdr ss) c-in))) “ 3.27 n (ripple-carry adder) . n . A1,A2,A3, ...,An B1, B2, B3, ..., Bn ( Ak Bk 0 1). n S1, S2, S3, ..., Sn , C . ripple-carry-adder . n --- Ak, Bk Sk--- , C . ”

- 38. * 1インバータ遅延(Di) * 1アンドゲート遅延(Da) * 1オアゲート遅延(Do) * Do >= Da + Di と仮定 半加算器の遅延: Sの遅延(Dhs) = max(Do, Da + Di) + Da = Do + Da Cの遅延(Dhc) = Da “ , . n , , , . ” 3.30 (RIPPLE-CARRY ADDER)

- 39. 3.30 (RIPPLE-CARRY ADDER) 半加算器 Sの遅延(Dhs) = Do + Da 半加算器 Cの遅延(Dhc) = Da 全加算器の遅延: Sの遅延(Dfs) = max(0, Dhs) + Dhs = 2Dhs = 2(Do + Da) = 2Do + 2Da Cの遅延(Dfc) = max(Dhs + Dhc, Dhc) + Do = Dhs + Dhc + Do = (Do + Da) + (Da) + Do = 2Do + 2Da “ , . n , , , . ”

- 40. 全加算器 Sの遅延(Dfs) = 2Do + 2Da 全加算器 Cの遅延(Dfc) = 2Do + 2Da n桁の繰上り伝播加算器: S1の遅延 Drs = (n-1) * Dfc + Dfs = (n-1) * (2Do + 2Da) + 2Do + 2Da = n(2Do + 2Da) = 2n(Do + Da) Cの遅延 Drc = (n-1) * Dfc + Dfc = n * Dfc = 2n(Do + Da) = n(2Do + 2Da) = 2n(Do + Da) 例: Di = 2, Da = 3, Do = 5 の時、 Drs = Drc = 2n(3 + 5) = 16n 3.30 (RIPPLE-CARRY ADDER) “ , . n , , , . ”

- 41. - 3.3.5 2017/06/07( ) 19:30 21:00 @3F - 🍕 🍣 connpass(http://sicp.iijlab.net/fulltext/x335.html )

- 42. SICP Structure and Interpretation of Computer Programs https://mitpress.mit.edu/sicp/full-text/book/book.html - HTML http://sicp.iijlab.net/fulltext/ - HTML minghai/sicp-pdf: SICP PDF with Texinfo and LaTeX source https://github.com/minghai/sicp-pdf - minghai hiroshi-manabe/sicp-pdf: SICP PDF with Texinfo and LaTeX source https://github.com/hiroshi-manabe/sicp-pdf - hiroshi-manabe SICP Lisper MIT SICP( ) - Qiita http://qiita.com/kaz-yos/items/d1ecd4bfe9989c290e99 SICP - sicp http://sicp.g.hatena.ne.jp/hyuki/ (SICP) - Higepon’s blog http://d.hatena.ne.jp/higepon/20061027/1161960363 (SICP) | http://kinokoru.jp/archives/794 ( ) https://web.archive.org/web/20150104041426/http://oss.timedia.co.jp/ show/SICP/Answer%20Book SICP-Solutions http://community.schemewiki.org/?SICP-Solutions