Internal microprocessor architecture

- 2. Group Members 12063122-011 ( M.Noman ) 12063122-017 ( Hafiz Hamid ) 12063122-029 ( Salah Uddin Ayubi ) 12063122-037 ( Mubashar Naeem ) 12063122-023 ( Safi ur rehman Tabasum ) University Of Gujrat (Pakistan)

- 3. Internal microprocessor architecture ON the basis of programing

- 4. Microprocessor’s type Internal structure of microprocessor should be known Single core 1. single task at any time 2.access whole memory at the same time by any program Dual core 1.multiple task at any time 2.access specific memory by any task

- 5. Programing model Program visible : 8086,8088 Registers are used directly during programing Program invisible : 80286 and above 1. Registers are not accessible directly during programing 2. Can be used indirectly

- 6. Programing model Program visible : 8086,8088 Registers are used directly during programing Program invisible : 80286 and above 1. Registers are not accessible directly during programing 2. Can be used indirectly

- 8. Only for 64 bit

- 9. cont.…. We can’t access these register with the instruction used to access general purpose register AX,BX etc…. To access the low order byte of R8 use R8B To access the low order word of R10 use R10W

- 10. Cont.……

- 11. Condition flag

- 12. Special purpose flag The 6 Segment Registers are: Stack Segment (SS). Pointer to the stack. Code Segment (CS). Pointer to the code. Data Segment (DS). Pointer to the data. Extra Segment (ES). Pointer to extra data ('E' stands for 'Extra'). F Segment (FS). Pointer to more extra data ('F' comes after 'E'). G Segment (GS). Pointer to still more extra data ('G' comes after 'F').

- 14. Remember R_ _ used in 64 bit MP E_ _ used in 32 bit MP (E stand for extended) Register can access as R_ _ , E_ _ , _ _ , _L ,_ H

- 15. Multipurpose or general purpose register

- 16. Accumulator (RAX) Used for IO operation, rotate, shift, multiplication and division

- 17. Base index (RBX) Hold the offset address of a location In a memory system Also address the memory data

- 18. Count Register (CX) Used as default counter for various instruction like repeated string, shift, rotate(CL), loop etc… Hold the offset address of memory data Address memory data

- 19. Data Register (DX) Hold the part of the result from a multiplication or part of the dividend before division. Address memory data

- 20. Stack Pointer : pointing the top of the stack in stack segment Base Pointer: contain the offset address within data segment Source index : Used as a pointer to a source in stream operations Destination index : used as a pointer to destination in stream operations All these register also used for based indexed, register indirect addressing

- 21. R8-R15 These register are only found in Pentium 4 and core2 if 64-bit extensions are enables Used as general purpose register In most application these registers remain unused

- 22. Special Purpose Register Instruction pointer (IP) : point to the next instruction in a program located within the code segment Stack Pointer : pointing the top of the stack in stack segment to store data

- 23. Flag Register Determine the current state of the process Modified automatically after M.Operations Conditional Flag Carry flag: indication of overflow condition for unsigned integer and hold carry Auxiliary flag : indication the carry/borrow from lower nibble to high nibble(D3-D4)

- 24. Parity flag : indication of parity of the result Zero : set if result is zero Sign flag: In signed magnitude format, if the result of the operation is negative, sign flag is set

- 25. Control Flag Control the operation of the execution unit Trap flag : if set, then debugging operation is allow Interrupt flag: control the operation of interrupt request. note : set by instruction STI clear by instruction CLI Direction flag : used in string operation. if it is set, string byte is accessed from higher memory address to lower memory address

- 26. Flags for 32,64-bit IOPL (IO privilege level) : used to select the privilege level for IO devices. if the current privilege level is 00 ,IO execute without hindrance if 11 then an interrupt occur and suspended the execution

- 27. NT (nested task) : indicate whether the task is nested with other or not RF (resume) : resume flag is used with debugging to control the resumption of execution after the next instruction

- 28. VM (virtual mode) : This allow the system program to execute multiple DOS operation AC (alignment check) : if the word or double word Is addressed on a non-word or non-double word boundary VIF (virtual interrupt flag) : copy the interrupt flag bit (in Pentium 4)

- 29. VIP (virtual interrupt pending) : Give the information about virtual mode interrupt. Set if interrupt is pending ID (identification) : The ID flag indicate that Pentium 4 micro- processor support the CPUID or not. The CPUID instruction provides the system with information about microprocessor such as its version number and manufacturer

- 30. Segment Register CS (code segment) : area of memory that hold the code (executable program) used by MP Have the starting address of the memory that hold code CS:IP used to access the whole 64k memory of code segment

- 31. SS (stack segment) : area of memory used for the stack stack is used to store data memory 64k can be access by SS:SP DS (data segment) : area of memory that hold all data refer by general purpose register (AX, BX etc. ) 64k memory Accessed by using DS and offset address register

- 32. ES (extra segment) : additional data segment that is used by some of the string instructions to hold destination data FS and GS : supplemental register used as most extra segment in 64-bit MP. Window use these segments for internal operation. But no definition for their usage is available

- 33. REAL MODE MEMORY ADDRESSING The only mode available on the 8086-8088. 20 bit address bus 1 MB, 16 bit data bus, 16 bit registers 80286 and above operate in either the real or protected mode. Real mode operation allows addressing of only the first 1M byte of memory space—even in Pentium 4 or Core2 microprocessor. the first 1M byte of memory is called the real memory, conventional memory, or DOS memory system

- 34. Segment registers hold the base address of where a particular segment begins in memory. There is the code segment (CS) data segment (DS) stack segment (SS) extra segment (ES).

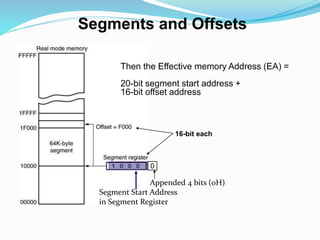

- 35. Segments and Offsets All real mode memory addresses must consist of a segment address plus an offset address. segment address defines the beginning address of any 64K-byte memory segment offset address selects any location within the 64K byte memory segment

- 36. Segments and Offsets 16-bit each Appended 4 bits (0H) Segment Start Address in Segment Register 0 Then the Effective memory Address (EA) = 20-bit segment start address + 16-bit offset address

- 37. – this shows a memory segment beginning at 10000H, ending at location IFFFFH • 64K bytes in length – also shows how an offset address, called a displacement, of F000H selects location 1F000H in the memory Segments and Offsets

- 38. Segments and Offsets Once the starting address is known, the ending address is found by adding FFFFH. because a real mode segment of memory is 64K in length The offset address is always added to the segment starting address to locate the data. [1000:2000H] a segment address of 1000H; an offset of 2000H

- 39. Effective Address Calculations • EA = segment register (SR) x 10H + offset (a) SR: 1000H 10000 + 0023 = 10023H (b) SR: AAF0H AAF00 + 0134 = AB034H (c) SR: 1200H 12000 + FFF0 = 21FF0H

- 41. Default Segment and Offset Registers The microprocessor has rules that apply to segments whenever memory is addressed. These define the segment and offset register combination [CS:IP] The code segment register defines the start of the code segment. The instruction pointer locates the next instruction within the code segment.

- 42. Default Segment and Offset Registers Another of the default combinations is the stack. stack data are referenced through the stack segment at the memory location addressed by either the stack pointer (SP) or the base pointer (BP) a memory segment can touch or overlap if 64K bytes of memory are not required for a segment

- 43. – think of segments as Windows that can be moved over any area of memory to access data or code – a program can have more than four or six segments, • but only access four or six segments at a time Default Segment and Offset Registers 00000 Stack Code Data Extra 0FFFF 10000 1FFFF 20000 2FFFF 30000 33FFF 34000 43FFF 44000 48FFF 49000 58FFF 59000 FFFFF Memory 1 0 0 0 DS 2 0 0 0 CS 3 4 0 0 SS 4 9 0 0 ES

- 44. Default Segment and Offset Registers Code should be limited to only this portion of the code segment, to avoid effects of segment overlap.

- 45. They can occupy completely separate parts of memory. Multiple segments could even coincide because there are multiple segment registers, the CPU can keep track of. A program can use, multiple segments at the same time.

- 47. Default Segment and Offset Registers Default segment numbers in: CS for program (code) SS for stack DS for data ES for string (destination) data Default offset addresses that go with them Convention Example: EA = CS:[IP] Segment Start in Segment register Offset: Literal or in a CPU register

- 49. TPA The Transient Program Area (TPA) holds the DOS (disk operating system) operating system; other programs that control the computer system. TPA is the first available area of memory above drivers and other TPA programs Area is indicated by a free-pointer maintained by DOS program loading is handled automatically by the program loader within DOS

- 50. The TPA also stores any currently active or inactive DOS application programs.

- 51. Real Mode Addressing Scheme Allows Relocation A relocatable program is one that can be placed into any area of memory and executed without change. Segment plus offset addressing allows DOS programs to be relocated in memory.

- 52. This mainly means using relative offsets for data accesses and jump instructions. If this is easy/possible is based on the type of architecture, the size of the address space and the size of the program.. Relocatable data are data that can be placed in any area of memory and used without any change to the program

- 53. Real Mode Addressing Scheme Allows Relocation Because memory is addressed within a segment by an offset address, the memory segment can be moved to any place in the memory system without changing any of the offset addresses. .

- 54. Only the contents of the segment register must be changed to address the program in the new area of memory. Windows programs are written assuming that the first 2G of memory are available for code and data.

![Segments and Offsets

Once the starting address is known, the ending

address is found by adding FFFFH.

because a real mode segment of memory is 64K in

length

The offset address is always added to the segment

starting address to locate the data.

[1000:2000H]

a segment address of 1000H; an offset of 2000H](https://image.slidesharecdn.com/internalmicroprocessorarchitecture-150203035614-conversion-gate01/85/Internal-microprocessor-architecture-38-320.jpg)

![Default Segment and Offset Registers

The microprocessor has rules that apply to

segments whenever memory is addressed.

These define the segment and offset register

combination

[CS:IP]

The code segment register defines the start of the

code segment.

The instruction pointer locates the next

instruction within the code segment.](https://image.slidesharecdn.com/internalmicroprocessorarchitecture-150203035614-conversion-gate01/85/Internal-microprocessor-architecture-41-320.jpg)

![Default Segment and Offset

Registers

Default segment numbers in:

CS for program (code)

SS for stack

DS for data

ES for string (destination) data

Default offset addresses that go with them

Convention Example: EA = CS:[IP]

Segment Start

in Segment register

Offset: Literal

or in a CPU register](https://image.slidesharecdn.com/internalmicroprocessorarchitecture-150203035614-conversion-gate01/85/Internal-microprocessor-architecture-47-320.jpg)