Logic Design - Book: Final notes without combinational

- 1. CHAPTER 1 5 NUMBER SYSTEMS AND CODES .............................5 INTRODUCTION ....................................................................... 5 BINARY NUMBERS .................................................................. 5 Binary to Decimal Conversion ................................................ 6 Decimal to Binary Conversion ................................................ 7 Range of binary numbers: ....................................................... 8 Binary Arithmetic .................................................................... 9 OCTAL NUMBERS .................................................................. 13 Octal Conversions ................................................................. 14 HEXADECIMAL NUMBERS .................................................. 17 Hexadecimal Conversion ....................................................... 18 1’S AND 2’S COMPLEMENTS .................................................. 20 REPRESENTATION OF SIGNED NUMBERS ....................... 21 Sign-Magnitude ..................................................................... 22 1’s Complement ..................................................................... 23 2’s Complement ..................................................................... 25 2's Complement Evaluation: .................................................. 28 ARITHMETIC OPERATIONS WITH SIGNED NUMBERS .. 30 Addition ................................................................................. 30 Subtraction ............................................................................ 33 BINARY CODED DECIMAL (BCD)....................................... 36 THE ASCII CODE .................................................................... 38 EXTENDED ASCII CHARACTERS ....................................... 40 THE EXCESS-3 CODE .................................................................. 42 Self-Complementing Property ............................................... 43 ERROR-DETECTION CODE .................................................. 44 QUESTIONS ............................................................................. 46 CHAPTER 2 51 LOGIC GATES 51 BOOLEAN VARIABLES & TRUTH TABLES ................................... 51 OR OPERATION .......................................................................... 52 Timing Diagrams of OR gates ............................................... 54 An application: Alarm System ............................................... 54 AND OPERATION ....................................................................... 55 Timing Diagrams of AND gates ............................................ 57 An application: A Seat Belt Alarm System ............................ 57 NOT OPERATION ........................................................................ 58 -1–

- 2. NOR OPERATION ....................................................................... 59 Negative AND equivalent of a NOR gate .............................. 60 An application: An aircraft landing indicator....................... 61 NAND OPERATION .................................................................... 62 Negative OR Equivalent Operation of the NAND Gate ........ 63 An application: An aircraft landing indicator....................... 64 THE EXCLUSIVE-OR AND EXCLUSIVE-NOR GATES...... 65 The Exclusive-OR Gate ......................................................... 65 The Exclusive-NOR Gate ....................................................... 66 Timing diagram ..................................................................... 67 INTEGRATED CIRCUIT LOGIC FAMILIES ......................... 67 Diode Logic (DL) .................................................................. 67 Resistor-Transistor Logic (RTL) ........................................... 69 Diode-Transistor Logic (DTL) .............................................. 70 Transistor-Transistor Logic (TTL) ........................................ 71 Emitter-Coupled Logic (ECL) ............................................... 73 CMOS Logic .......................................................................... 73 Fan-in .................................................................................... 77 Fan-out .................................................................................. 77 Comparison of performance characteristics of CMOS, TTL and ECL logic gates. ............................................................. 77 QUESTIONS ............................................................................. 78 CHAPTER 3 84 BOOLEAN ALGEBRA ............................................... 84 DESCRIBING LOGIC CIRCUITS ALGEBRAICALLY ......................... 84 EVALUATING LOGIC CIRCUIT OUTPUTS ..................................... 85 IMPLEMENTING CIRCUITS FROM BOOLEAN EXPRESSION ............ 87 BOOLEAN THEOREMS ................................................................. 88 DEMORGAN'S THEOREM ............................................................ 91 UNIVERSALITY OF NAND & NOR GATES ................................. 94 ALTERNATE LOGIC GATE REPRESENTATIONS ............................ 96 LOGIC SYMBOL INTERPRETATION............................................... 98 CANONICAL AND STANDARD FORMS ............................. 98 Minterms and Maxterms ........................................................ 99 Sum of Minterms .................................................................. 102 Product of Maxterms ........................................................... 103 STANDARD FORMS ........................................................... 104 QUESTIONS ............................................................................... 105 -2–

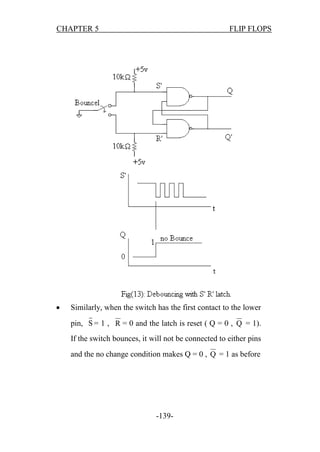

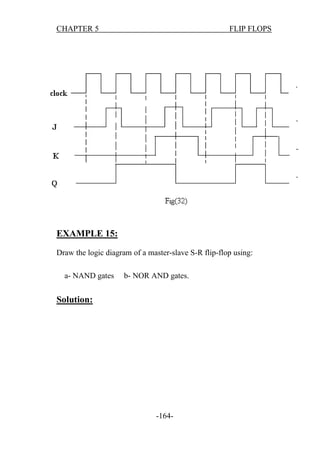

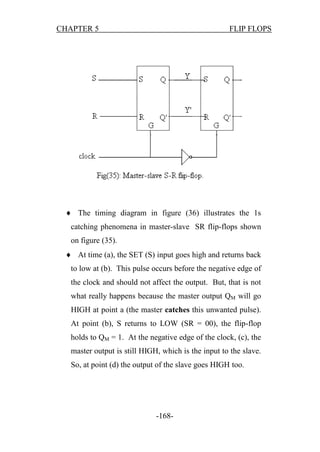

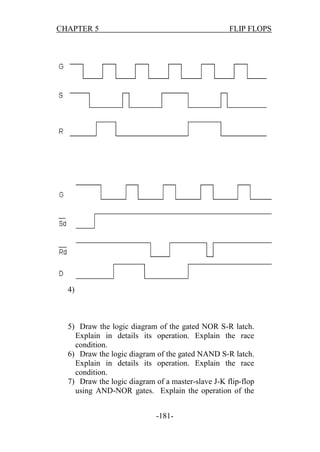

- 3. CHAPTER 4 110 THE KARNAUGH MAP .......................................... 110 THE THREE VARIABLE KARNAUGH MAP...................... 110 THE FOUR VARIABLE KARNAUGH MAP ........................ 111 KARNAUGH MAP SIMPLIFICATION OF SOP EXPRESSIONS ........ 111 DETERMINING THE MINIMUM SOP EXPRESSION FROM THE MAP ................................................................................................. 112 KARNAUGH MAP PRODUCT OF SUM (POS) SIMPLIFICATION ................................................................. 115 DON'T CARE CONDITIONS ................................................. 117 QUESTIONS: .......................................................................... 120 CHAPTER 5 122 SEQUENTIAL LOGIC AND FLIP-FLOPS ........... 122 INTRODUCTION ................................................................... 122 SEQUENTIAL CIRCUITS AND FEEDBACK: ..................... 122 Cross- NOR S-R latch ( active high ) .................................. 124 Cross- NAND S-R latch . ( active low ). .............................. 129 S – R Timing Analysis : ....................................................... 134 Switch Debouncing Circuits : .............................................. 137 STATE : ................................................................................... 142 CLOCKED SR LATCHES ( FLIP – FLOPS ) : .................................. 143 GATED D LATCH : ................................................................... 146 Integrated – circuit D latch ( 7475 ) : ................................. 147 J–K FLIP – FLOPS : ................................................................ 149 T. (TOGGLE) FLIP–FLOP ..................................................... 153 MASTER – SLAVE FLIP-FLOPS : ........................................ 155 EDGE – TRIGGERED J K FFS : ............................................. 159 MASTER-SLAVE FLIP-FLOP AND 1S CATCHING:.......... 167 DIRECT ( ASYNCHRONOUS ) INPUTS : ............................ 172 FLIP- FLOP OPERATING CHARACTERISTICS ................ 176 Propagation Delay times: .................................................... 176 SET-UP TIME ..................................................................... 178 HOLD TIME ........................................................................ 178 QUESTIONS ........................................................................... 180 CHAPTER 6 185 SEQUENTIAL CIRCUIT ANALYSIS AND DESIGN ....................................................... 185 -3–

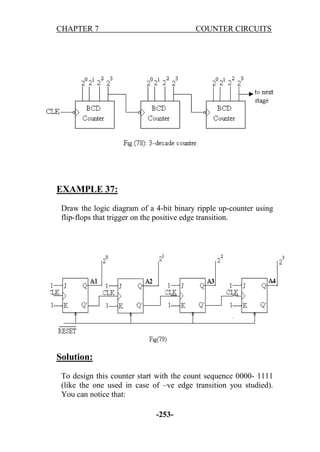

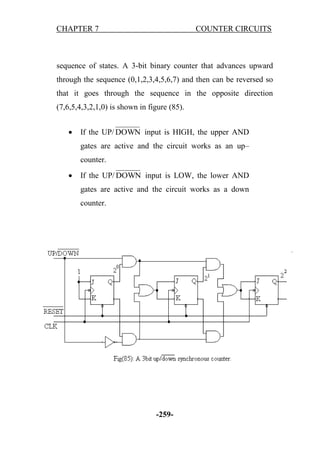

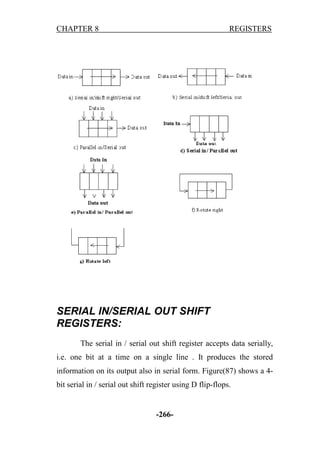

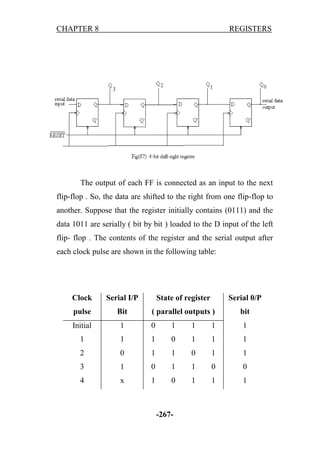

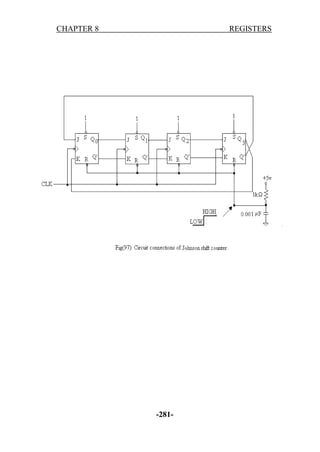

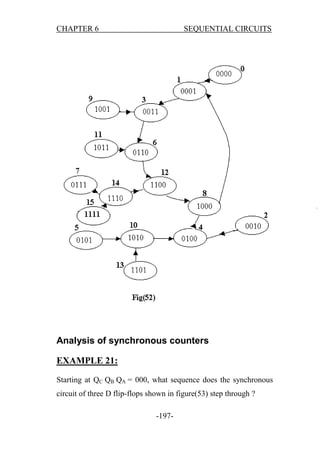

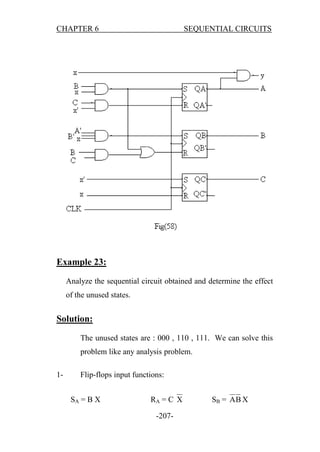

- 4. FLIP-FLOP EXCITATION TABLES : ................................... 185 BASIC DEFINITIONS OF SEQUENTIAL CIRCUITS ......... 188 Sequential circuit : .............................................................. 188 State Versus Output: ............................................................ 188 Moore Circuits (Fig (46)) : ................................................. 188 Mealy Circuits: .................................................................... 189 COUNTERS ................................................................................ 190 STATE DIAGRAM: ..................................................................... 190 ANALYSIS OF A SEQUENTIAL CIRCUIT : ....................... 192 Analysis of synchronous counters........................................ 197 DESIGN OF SEQUENTIAL CIRCUITS : .............................. 200 Design with unused states : ................................................. 203 Design of counters : ............................................................. 210 QUESTIONS ........................................................................... 238 CHAPTER 7 242 COUNTER CIRCUITS ............................................. 242 CLASSIFICATION OF COUNTERS ..................................... 242 RIPPLE COUNTERS (ASYNCHRONOUS COUNTERS):... 243 3-bit Asynchronous Binary counter : (Mod-8) .................... 243 COUNT SEQUENCE .................................................................... 244 DOWN COUNTERS: .............................................................. 246 DESIGN OF DIVIDE – BY – N COUNTERS: ....................... 248 BCD RIPPLE (DECADE) COUNTER ................................... 251 SYNCHRONOUS COUNTERS: ............................................ 255 SYNCHRONOUS BINARY DOWN-COUNTER: ................ 258 UP/DOWN SYNCHRONOUS COUNTERS: ......................... 258 QUESTIONS ........................................................................... 260 CHAPTER 8 REGISTERS 263 263 REGISTER WITH PARALLEL LOAD : ................................ 263 SHIFT REGISTER BASICS: .................................................. 265 SERIAL IN/SERIAL OUT SHIFT REGISTERS: ................... 266 PARALLEL IN/SERIAL OUT SHIFT REGISTERS.............. 269 BIDIRECTIONAL SHIFT REGISTER: ................................. 273 RING SHIFT COUNTER AND JOHNSON SHIFT COUNTER: ................................................................................................. 277 Ring shift counter operation ................................................ 279 Johnson shift counter operation .......................................... 280 -4–

- 5. CHAPTER 1 NUMBER SYSTEMS AND CODES CHAPTER 1 NUMBER SYSTEMS AND CODES DIGITAL SYSTEM INTRODUCTION You have previously studied how to represent a number in decimal, binary, octal and hexadecimal numbering systems and also how to make a conversion from one representation to the other ones. In the following sections, we will make a quick overview of these skills. Then, we will illustrate how to represent negative numbers in binary and how to make arithmetic operations on them. After that a group of the most used codes and their common uses are given. Finally, two famous and simple error correction and detection codes are given. BINARY NUMBERS In the well known decimal numbering system, each position can represent 10 different digits from 0 to 9. each position has a weighting factor of powers of 10. -5–

- 6. CHAPTER 1 NUMBER SYSTEMS AND CODES Example: To Evaluate (5621)10 each digit is multiplied by the weight of its position which is a power of 10. 5621 = 1x100 + 2x101 + 6x102 + 5x103 A similar approach is followed in the other numbering systems with a variation in the base (10, 2, 8, 16). In binary numbers, we can only use the digits 0 and 1 and the weights are powers of 2. Table[I] 210 29 28 1024 512 256 27 128 26 64 25 32 24 16 23 8 22 4 21 2 20 1 Binary to Decimal Conversion To convert a binary number into decimal, we multiply each bit (binary digit) by the weight of its position and sum up the results. Example: Convert the binary number (11011011)2 to decimal. Answer: -6–

- 7. CHAPTER 1 NUMBER SYSTEMS AND CODES (11011011)2 = 1x 20+ 1x 21+ 1x 23+ 1x 24+ 1x 26+ 1x27 = 1 + 2 + 8 +16 + 64 + 128 = 219 Decimal to Binary Conversion There are two ways to make this conversion; the repeated division-by-2-method (which you have studied before) and the sum of weights method (which will be illustrated now). Sum of weights method: To find a binary number that is equivalent to a decimal number, we can determine the set of binary weights whose sum is equal to the decimal number. We can use table[I] to determine the highest weight that is less than the number and put 1 in its position then subtracting it from the number and repeating the same process until finding all the 1s in the number then filling the positions in between with 0s. Example: Convert the following decimal numbers to binary form: 13, 100, 65, and 189. Put your answer as eight bit numbers. Answer: 13 = 128 0 64 0 32 0 -7– 16 0 8 1 4 1 2 0 1 1

- 8. CHAPTER 1 NUMBER SYSTEMS AND CODES 100 = 65 = 189 = 0 0 1 1 1 0 1 0 1 0 0 1 0 0 1 1 0 1 0 0 0 0 1 1 Range of binary numbers: We have used eight bit numbers for illustration because the 8-bit grouping is standard in most computers and has been given the special name byte. Using eight bits, 256 different numbers can be represented. Combining two bytes to get sixteen bits, 65,536 different numbers can be represented. Combining four bytes to get 32 bits, 4.295 X 109 different numbers can be represented, and so on. The formula for finding the number of different combinations of n bits is Total combinations = 2n different numbers in the range 0 to (2n – 1) For example a 4-bit number can hold up to 2 =16 different values in the range 0 to 15 (0 to 1111). An 8-bit number can hold up to 28=256 different values in the range 0 to 255 (0 to 11111111). 4 Example: What is the range of values (in decimal) that can be represented by a binary number of the following number of bits: 10, 20 and 24. Solution: N=10 range = 0 to 210 – 1 = 0 to 1023 i.e. 1024 (1K)numbers -8–

- 9. CHAPTER 1 NUMBER SYSTEMS AND CODES N=20 range = 0 to 220 – 1 = 0 to 1048575 i.e. 1048576 (1M)numbers N=24 range = 0 to 224 – 1 = 0 to 16777215 i.e. 16777216 (16M)numbers Binary Arithmetic Binary Addition The four cases for adding binary digits (A + B) are as follows: A 0 0 1 1 B 0 1 0 1 S 0 1 1 0 C 0 0 0 1 Where: S is the sum and C is the carry. Example: Add the following binary numbers and put the result in 8-bits. Verify your answer by converting into decimal: a) 00111111 + 01111100 b) 11101101 + 01000011 Answer: a) 00111111 + 01111100 = 10111011 187) -9– (63 + 124 =

- 10. CHAPTER 1 NUMBER SYSTEMS AND CODES b) 11101101 + 01000011 = 100110000 This example shows that the result could not fit in 8-bits ( 237 + 67 = 304) and the maximum capacity of 8-bits is 255. That is what we call overflow. 1 0 0 1 1 0 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 1 0 1 1 1 1 1 1 1 0 0 1 0 0 1 0 0 1 1 1 1 0 0 1 1 0 0 1 0 1 1 1 0 0 Binary Subtraction The four cases for subtracting binary digits (A B) are as follows: A 0 0 1 1 B 0 1 0 1 D 0 1 1 0 B 0 1 0 0 Where: D is the difference and B is the borrow. Example: Subtract the following binary numbers and put the result in 8-bits. Verify your answer by converting into decimal: a) 10111111 - 01111100 b) 11101101 - 01000011 - 10 –

- 11. CHAPTER 1 NUMBER SYSTEMS AND CODES Answer: a) 10111111 - 01111100 = 01000011 (191 - 124 = 67) b) 11101101 - 01000011 = 10101010 (237 – 67 = 170) 0 1 0 0 10 0 1 1 1 1 1 1 1 1 1 1 1 0 0 1 0 0 0 0 1 1 0 10 1 1 1 0 1 1 0 1 0 1 0 0 0 0 1 1 1 0 1 0 1 0 1 0 Binary Multiplication The four cases for multiplying binary digits (A x B) are as follows: A 0 0 1 1 B 0 1 0 1 P 0 0 0 1 Where: P is the product. Example: Multiply the following binary numbers and put the result in 8-bits. Verify your answer by converting into decimal: a) 11100 x 101 b) 11011 x 1101 - 11 –

- 12. CHAPTER 1 NUMBER SYSTEMS AND CODES Answer: a) 11100 x 101 = 10001100 (16+8+4) x (4+1) = (128+8+4) 28 x 5 = 140 b) 11011 x 1101 = 101011111 (16+8+2+1) x (8+4+1) = (256+64+16+8+4+2+1) 27 x 13 = 351 This case indicates a condition of overflow, where the resulting number (351) could not fit in 8-bits and we need an extra bit to represent it correctly. 1 1 1 0 0 1 1 0 1 1 1 0 1 1 1 0 1 1 1 1 0 0 1 1 0 1 1 0 0 0 0 0 1 1 1 0 0 0 0 0 0 0 1 1 0 1 1 1 0 0 0 1 1 0 0 1 1 0 1 1 1 0 1 0 1 1 1 1 1 Binary Division Division in binary numbers is similar to long division in decimal. - 12 –

- 13. CHAPTER 1 NUMBER SYSTEMS AND CODES Example: Divide the following binary numbers and put the result in 8-bits. Verify your answer by converting into decimal: 11001 ÷ 101 Answer: a) 11001 ÷ 101 = 101 (16+8+1) ÷ (4+1) = (4+1) 25 ÷ 5 = 5 1 0 1 1 0 1 1 1 0 0 1 1 0 1 1 0 1 1 0 1 0 0 0 OCTAL NUMBERS The eight allowable digits are 0,1,2,3,4,5,6 and 7 and the weights are powers of 8. Decimal Binary Octal 0 1 2 0 1 2 000 001 010 - 13 –

- 14. CHAPTER 1 3 4 5 6 7 8 9 10 11 NUMBER SYSTEMS AND CODES 011 100 101 110 111 1000 1001 1010 1011 3 4 5 6 7 10 11 12 13 Octal Conversions Converting from binary to octal is simply a matter of grouping the binary positions in groups of three (starting at the least significant position) and writing down the octal equivalent. Example Convert the following binary numbers into octal: a) 10110111 b) 01101100 Solution: a) 10110111 = 010 101 111 = 257 (add a zero to the left and start from the least significant bit (LSB) make groups of three bits and convert each group into octal) b) 01101100 = 001 101 100 = 154 - 14 –

- 15. CHAPTER 1 NUMBER SYSTEMS AND CODES Example Convert the following octal number into binary: a) 327 b)601 Solution: a) 327 = 011 010 111 = 11010111 (replace each octal number with three equivalent binary numbers even if the number can be represented by less than three bits) b) 601 = 110 000 001 = 110000001 To convert from octal to decimal, (multiply by weighting factors). Example: Convert 713 to decimal. Solution: 713 = 7 x 82 + 1 x 81 + 3 x 80 = 459 To convert from decimal to octal, the successive-division procedure or the sum of weights procedure can be used. - 15 –

- 16. CHAPTER 1 NUMBER SYSTEMS AND CODES Example Convert the following decimal numbers to octal: a) (596)10 b) (100)10 Solution: 596 = 1000 = 83 82 81 512 64 8 1 1 2 1 7 5 80 1 4 0 a) 596 ÷ 8 = 74 remainder 4 74 ÷ 8 = 9 remainder 2 1124 9 ÷ 8 = 1 remainder 1 1 ÷ 8 = 0 remainder 1 b) 1000 ÷ 8 = 125 remainder 0 125 ÷ 8 = 15 remainder 5 15 ÷ 8 = 1 remainder 7 1 ÷ 8 = 0 remainder 1 - 16 – 1750

- 17. CHAPTER 1 NUMBER SYSTEMS AND CODES HEXADECIMAL NUMBERS The 16 allowable digits are 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E and F and the weights are powers of 16. Decimal 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 Binary 0000 0000 0000 0001 0000 0010 0000 0011 0000 0100 0000 0101 0000 0110 0000 0111 0000 1000 0000 1001 0000 1010 0000 1011 0000 1100 0000 1101 0000 1110 0000 1111 0001 0000 0001 0001 0001 0010 0001 0011 0001 0100 Hexadecimal 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10 11 12 13 14 - 17 –

- 18. CHAPTER 1 NUMBER SYSTEMS AND CODES Hexadecimal Conversion Converting from binary to hexadecimal is simply a matter of grouping the binary positions in groups of four (starting at the least significant position) and writing down the hexadecimal equivalent. Example Convert the following binary numbers into hexadecimal: a) 10101111 b) 01101100 Solution: a) 10110111 = 1011 0111 = (B 7)16 b) 01101100 = 0110 1100 = (6 C)16 Example Convert the following hexadecimal number into binary: a) A2E b)60F Solution: a) (A2E)16 = 1010 0010 1110 = (101000101110)2 (replace each hexadecimal number with four equivalent binary numbers even if the number can be represented by less than four bits) - 18 –

- 19. CHAPTER 1 NUMBER SYSTEMS AND CODES b) (60F)16 = 0110 0000 1111 = (011000001111)2 To convert from hexadecimal to decimal, (multiply by weighting factors). Example: Convert (7AD)16 to decimal. Solution: (7AD)16 = 7 x 162 + 10 x 161 + 13 x 160 = (1965)10 To convert from decimal to hexadecimal, the successive-division procedure or the sum of weights procedure can be used. Example Convert the following decimal numbers to hexadecimal: a) (596)10 b) (100)10 Solution: 596 = 1000 = 162 161 160 256 16 1 2 5 4 3 E 8 a) 596 ÷ 16 = 37 remainder 4 37 ÷ 8 = 4 remainder 5 - 19 – 554

- 20. CHAPTER 1 NUMBER SYSTEMS AND CODES 5 ÷ 8 = 0 remainder 5 b) 1000 ÷ 16 = 62 remainder 8 62 ÷ 16 = 3 remainder 14 3E8 3 ÷ 16 = 0 remainder 3 1’s and 2’s COMPLEMENTS 1’s and 2’s complement allow the representation of negative numbers in binary. In most computers 2’s complement is used to represent negative numbers. The 1's complement of a binary number is found by simply changing all 1s to 0s and all 0s to 1s. Example: Obtain the 1’s complement of the following binary numbers: 10001111, 01101100 and 00110011 Solution The 1’s complement of 10001111 = 01110000 . The 1’s complement of 01101100 = 10010011 . The 1’s complement of 00110011 = 11001100 . The 2's complement of a binary number is found by adding 1 to the LSB of the 1 's complement. Another way of obtaining the 2’s complement of a binary number is to start with the LSB (the rightmost bit) and leave the bits unchanged until you find the first - 20 –

- 21. CHAPTER 1 NUMBER SYSTEMS AND CODES 1. Leave the first 1 unchanged and complement the rest of the bits (change 0 to 1 and 1 to 0). Example: Obtain the 2’s complement of the following binary numbers: 10001111, 01101100 and 00110011 Solution The 2’s complement of 10001111 = 01110000 +1 = 01110001 The 2’s complement of 01101100 = 10010011 + 1 = 01101101 The 2’s complement of 00110011 = 11001100 + 1 = 00110100 To convert from a 1's or 2's complement back to the true (uncomplemented) binary form, use the two procedures described previously. To go from the 1s complement back to true binary, reverse all the bits. To go from the 2's complement form back to true binary, take the 1's complement and add 1 to the least significant bit. REPRESENTATION OF SIGNED NUMBERS Computer, must be able to handle both positive and negative numbers. There are three basic ways to represent signed numbers; sign-magnitude, 1’s complement and 2’s complement. - 21 –

- 22. CHAPTER 1 NUMBER SYSTEMS AND CODES Sign-Magnitude The number consists of two parts: the MSB (most significant bit) represents the sign and the other bits represent the magnitude of the number. If the sign bit is 1 the number is negative and if it is 0 the number is positive. To illustrate this let us have an example. Example: Express each of the following numbers as an 8-bit number in sign-magnitude form: -30, 30, -121 and +99. Solution: -30 = 1 0011110 (The leftmost 1 indicates that the number is negative. The remaining 7bits carry the magnitude of 30) 30 = 0 0011110 (The only difference between –30 and +30 is the sign bit because the magnitude bits are similar in both numbers.) -121 = 1 1111001 99 = 0 1100011 - 22 –

- 23. CHAPTER 1 NUMBER SYSTEMS AND CODES Example: Find the decimal value of each of the following numbers if they are expressed in sign-magnitude form: 10111001 , 11111111 and 01111111. Solution: 10111001 = -57 (The leftmost 1 indicates that the number is negative. The remaining 7bits carry the magnitude of 57) 11111111 = -127 (The minimum number that can be represented in an 8-bit register using sign-magnitude representation) 01111111 = +127 (The maximum number that can be represented in an 8-bit register using sign-magnitude representation) Range of numbers in Sign-Magnitude Representation: In general for an n-bit number, the range of values that could be represented using sign-magnitude notation is from –(2n-1-1) to +(2n-1-1). For example if n=8 the range is from –127 to 127. 1’s Complement Negative numbers are represented in 1’s complement format whereas positive numbers are represented as the positive sign-magnitude numbers - 23 –

- 24. CHAPTER 1 NUMBER SYSTEMS AND CODES Example: Express each of the following numbers as an 8-bit number in 1’s complement form: 30, -30, -121 and +99. Solution: 30 = 00011110 -30 = 11100001 (the number equals the 1’s complement of 30) 121 = 01111001 -121 = 10000110 99 = 01100011 Example: Find the decimal value of each of the following numbers if they are expressed in 1’s complement form: 10111001 , 11111111 ,10000000 and 01111111. Solution: 10111001 = -01000110 = -70 (The leftmost 1 indicates that the number is negative. Take the 1’s complement of the number to get the magnitude of 70) - 24 –

- 25. CHAPTER 1 NUMBER SYSTEMS AND CODES 11111111 = -00000000 = -0 (That is one of the problem of 1’s complement representation, there are two representations of zero a positive one and a negative one.) 01111111 = +127 (The maximum number that can be represented in an 8-bit register using 1’s complement representation) 10000000 = -01111111 = -127 (The maximum number that can be represented in an 8-bit register using 1’s complement representation) Range of numbers Representation: in 1’s complement It is exactly the same as the range of numbers in sign-magnitude. 2’s Complement Negative numbers are represented in 2’s complement format whereas positive numbers are represented exactly the same way as in sign-magnitude and in 1’s complement. Example: Express each of the following numbers as an 8-bit number in 2’s complement form: 30, -30, -121 and +99. - 25 –

- 26. CHAPTER 1 NUMBER SYSTEMS AND CODES Solution: 30 = 00011110 -30 = 11100010 (the number equals the 2’s complement of 30) 121 = 01111001 -121 = 10000111 99 = 01100011 Example: Find the decimal value of each of the following numbers if they are expressed in 2’s complement form: 10111001 , 11111111 ,10000000 and 01111111. Solution: 10111001 = -01000111 = -71 (The leftmost 1 indicates that the number is negative. Take the 2’s complement of the number to get the magnitude of 71) 11111111 = -00000001 = -1 (The problem of two representations of zero is not found in 2’s complement.) 01111111 = +127 (The maximum number that can be represented in an 8-bit register using 2’s complement representation) - 26 –

- 27. CHAPTER 1 NUMBER SYSTEMS AND CODES 10000000 = -10000000 = -128 (The minimum number that can be represented in an 8-bit register using 2’s complement representation) Range of numbers Representation: in 2’s complement In general for an n-bit number, the range of values that could be represented using 2’s complement notation is from –(2n-1) to +(2n-1-1). For example if n=8 the range is from –128 to 127. You may note from the previous examples that a binary number may have different values depending on the type of representation used to interpret this number. The following table clarifies this fact for a 4-bit binary number. 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 unsigned Signmagnitude 0 0 1 1 2 2 3 3 4 4 5 5 6 6 7 7 8 -0 9 -1 10 -2 11 -3 12 -4 13 -5 - 27 – 1’s complement 0 1 2 3 4 5 6 7 -7 -6 -5 -4 -3 -2 2’s complement 0 1 2 3 4 5 6 7 -8 -7 -6 -5 -4 -3

- 28. CHAPTER 1 NUMBER SYSTEMS AND CODES 1110 14 1111 15 -6 -7 -1 -0 -2 -1 2's Complement Evaluation: Positive and negative numbers in the 2's complement system are evaluated by summing the weights in all bit positions where there are 1s and ignoring those positions where there are zeros. The weight of the sign bit in a negative number is given a negative value. EXAMPLE Determine the decimal values of the signed binary numbers expressed in 2's complement: (a) 01010110 (b) 10101010. Solution (a) The bits and their powers-of-two weights for the positive number are as follows: -27 26 25 24 23 22 21 2° 0 1 0 1 0 1 1 0 Summing the weights where there are 1's, - 28 –

- 29. CHAPTER 1 NUMBER SYSTEMS AND CODES 64 + 16 + 4 + 2 = +86 (b) The bits and their powers-of-two weights for the negative number are as follows. Notice that the negative sign bit has a weight of —27 = —128. -27 26 25 24 23 22 21 2° 1 0 1 0 1 0 1 0 Summing the weights where there are 1's, -128 + 32 + 8 + 2 = -86 From these examples, you can see one of the reasons why the 2's complement system is preferred for representing signed numbers: It simply requires a summation of weights regardless of whether the number is positive or negative. The sign-magnitude system requires two steps—sum the weights of the magnitude bits and examine the sign bit to determine if the number is positive or negative. The 1's complement system requires adding 1 to the summation of weights for negative numbers but not for positive numbers. - 29 –

- 30. CHAPTER 1 NUMBER SYSTEMS AND CODES Also, the 1's complement system is generally not used because two representations of zero (00000000 or 11111111) are possible. The 2's complement system is preferred and is used in most computers because it makes arithmetic operations easier, as you will see. ARITHMETIC OPERATIONS WITH SIGNED NUMBERS In the last section, you learned how signed numbers are represented in three different systems. In this section, you will learn how signed numbers are added and subtracted. Because the 2's complement system for representing signed numbers is the most widely used in computers and microprocessor-based systems, the coverage in this section is limited to 2 's complement arithmetic. The processes covered can be extended to the other systems if necessary. Addition The two numbers in an addition are the addend and the augend. The result is the sum. There are four cases that can occur when two signed binary numbers are added: 1. Both numbers positive 2. Positive number with magnitude larger than negative number - 30 –

- 31. CHAPTER 1 NUMBER SYSTEMS AND CODES 3. Negative number with magnitude larger than positive number 4. Both numbers negative Let's take one case at a time using 8-bit signed numbers as examples. The equivalent decimal numbers are shown for reference. Both numbers positive: 00000111 7 + 00000100 +4 00001011 11 The sum is positive and is therefore in true (uncomplemented) binary. Positive number with magnitude larger than negative number: 00001111 + 11111010 Discard carry —————1 15 + -6 00001001 9 The final carry bit is discarded. The sum is positive and therefore in true (uncomplented) binary. - 31 –

- 32. CHAPTER 1 NUMBER SYSTEMS AND CODES Negative number with magnitude larger than positive number: 00010000 + 11101000 11111000 16 + -24 -8 The sum is negative and therefore in 2's complement form. Discard carry—————> 11111011 —5 + 11110111 Both numbers negative: + -9 1 11110010 -14 The final carry bit is discarded. The sum is negative and therefore in 2's complement form.In a computer, the negative numbers are stored in 2's complement form so, as you can see, the addition process is very simple: Add the two numbers and discard any final carry bit. Overflow Condition When two numbers are added and the number of bits required to represent the sum exceeds the number of bits in the two numbers, an overflow results as indicated - 32 –

- 33. CHAPTER 1 NUMBER SYSTEMS AND CODES by an incorrect sign bit. An overflow can occur only when both numbers are positive or both numbers are negative. The following 8-bit example will illustrate this condition. 01111101 125 + 00111010 + 58 10110111 183 Sign incorrect Magnitude incorrect In this example the sum of 183 requires eight magnitude bits. Since there are seven magnitude bits in the numbers (one bit is the sign), there is a carry into the sign bit which produces the overflow indication. Numbers Are Added Two at a Time Subtraction Subtraction is a special case of addition. For example, subtracting +6 (the subtrahend from +9 (the minuend) is equivalent to adding —6 to +9. Basically, the subtraction operation changes the sign of the subtrahend and adds it to the minuend. The result of a subtraction is called the difference. - 33 –

- 34. CHAPTER 1 NUMBER SYSTEMS AND CODES The sign of a positive or negative binary number is changed by taking its 2's complement. For example, taking the 2's complement of the positive number 00000100 (+4), you get 11111100, which is —4 as the following sum-of-weights evaluation shows: -128 + 64 + 32 + 16 + 8 + 4 = -4 As another example, taking the 2's complement of the negative number 11101101 (—19), you get 00010011, which is +19 as the following evaluation shows: 16 + 2+ 1 = 19 Since subtraction is simply an addition with the sign of the subtrahend changed, the process is stated as follows: To subtract two signed numbers, take the 2's complement of the subtrahend and add, discarding any final carry bit. EXAMPLE Perform each of the following subtractions of the signed numbers: (a) 00001000 - 00000011 (b) 00001100 - 11110111 - 34 –

- 35. CHAPTER 1 NUMBER SYSTEMS AND CODES (c) 11100111 - 00010011 (d) 10001000 - 11100010 Solution Like in other examples, the equivalent decimal subtractions are given for reference. (a) In this case, 8 - 3 = 8 + (-3) = 5. 00001000 + 11111101 Minuend (+8) 2's complement of subtrahend (-3) Discard carry —> 1 00000101 Difference (+ 5) (b) In this case, 12 - (-9) = 12 + 9 = 21. 00001100 + 00001001 00010101 Minuend (+12) 2's complement of subtrahend (+9) Difference (+21) (c) In this case, -25 - (+19) = -25 + (-19) = -44. 11100111 Minuend (-25) - 35 –

- 36. CHAPTER 1 NUMBER SYSTEMS AND CODES + 11101101 2's complement of subtrahend (- 19) Discard carry —>1 11010100 Difference (-44) (d) In this case, -120 - (-30) = -120 + 30 = -90 10001000 + 00011110 Minuend (-120) 2's complement of subtrahend (+30) 10100110 Difference (-90) BINARY CODED DECIMAL (BCD) The binary coded decimal system is used to represent each of the ten decimal digits as a 4-bit binary code. This code is useful in dealing with decimal numbers. As you know a 4-bit binary number can represent up to 16 numbers (0-15) but there are only 10 decimal digits (0-9), so we have 6 representations (1015) which are not used in the BCD code. To convert a decimal number to BCD replace each digit with a corresponding 4-bit binary number even if the number can be represented by less than 4 bits. To convert a BCD number into decimal make groups of 4 bits starting from the LSB, if necessary add extra zeroes to the left then convert each 4-bits to decimal. Decimal 0 1 2 BCD 0000 0001 0010 - 36 –

- 37. CHAPTER 1 3 4 5 6 7 8 9 NUMBER SYSTEMS AND CODES 0011 0100 0101 0110 0111 1000 1001 Example: Convert the following decimal numbers to BCD: 125, 909 and 1476. Solution: (125)10 = 0001 0010 0101 (909)10 = 1001 0000 1001 (1476)10 = 0001 0100 0111 0110 Example: Convert the following BCD numbers to decimal: 100000101001, 1101110010, 110010000101. Solution: 1000 0010 1001 = (825)10 0011 0111 0010 = (372)10 - 37 – 1010000101 and

- 38. CHAPTER 1 NUMBER SYSTEMS AND CODES 0010 1000 0101= (285)10 1100 1000 0101 = This number can not be a BCD number because 1100 is the binary representation of 12 and this is not a valid decimal digit. THE ASCII CODE To get information into and out of a computer, we need more than just numeric representations; we also have to take care of all the letters and symbols used in day-to-day processing. Information such as names, addresses, and item descriptions must be input and output in a readable format. But remember that a digital system can deal only with 1's and 0's. Therefore, we need a special code to represent all alphanumeric data (letters, symbols, and numbers). Most industry has settled on an input/output (I/O) code called the American Standard Code for Information Interchange (ASCII). The ASCII code uses 7 bits to represent all the alphanumeric data used in computer I/O. Seven bits will yield 128 different code combinations, as listed in the following Table. Each time a key is depressed on an ASCII keyboard, that key is converted into its ASCII code and processed by the computer. Then, before outputting the computer contents to a display terminal or printer, all information is converted from ASCII into standard English. - 38 –

- 39. CHAPTER 1 NUMBER SYSTEMS AND CODES ASCII control characters Name NUL SOH STX ETX EOT ENQ ACK BEL BS HT LF VT FF CR SO SI DLE DC1 DC2 DC3 DC4 NAK SYN ETB CAN EM SUB ESC FS GS RS Decimal 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 . 27 28 29 30 Hex 00 01 02 03 04 05 06 07 08 09 OA OB OC OD OE OF 10 11 12 13 14 15 16 17 18 19 1A 1B 1C ID 1E - 39 – ..Key, CTRL@ CTRL A CTRL B CTRL C CTRL D CTRL E CTRL F CTRL G CTRL H CTRL I CTRL J CTRL K CTRL L CTRL M CTRL N CTRL O CTRL P CTRL Q CTRL R CTRL S CTRL T CTRL U CTRL V CTRL W CTRL X CTRL Y CTRL Z CTRL [ CTRL / CTRL ] CTRL^ Description null character start of header start of text end of text end of transmission enquire acknowledge bell backspace horizontal tab line feed vertical tab form feed (new page) return carriage shift out shift in data link escape device control 1 device control 2 device control 3 device control 4 negative acknowledge synchronize end of transmission cancel block medium end of substitute escape file separator group separator record separator

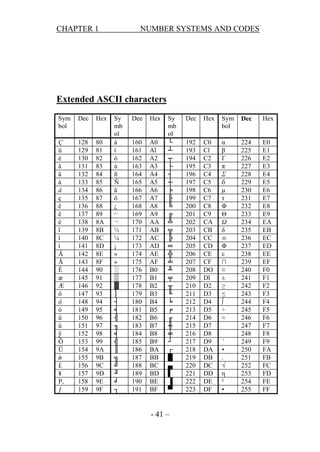

- 40. CHAPTER 1 US NUMBER SYSTEMS AND CODES 31 IF CTRL_ unit separator EXTENDED ASCII CHARACTERS In addition to the 128 standard ASCII characters, there are an additional 128 characters that were adopted by IBM for use in their PCs. Because of the popularity of the PC, these particular extended ASCII characters are also used in applications other than PCs and have become essentially an unofficial standard. The extended ASCII characters are represented by an 8-bit code series from hexadecimal 80 to hexadecimal FF. The extended ASCII contains characters in the following general categories: 1. Foreign (non-English) alphabetic characters 2. Foreign currency symbols 3. Greek letters 4. Mathematical symbols 5. DRAWING CHARACTERS 6. Bar graphing characters 7. Shading characters - 40 –

- 41. CHAPTER 1 NUMBER SYSTEMS AND CODES Extended ASCII characters Sym bol Dec Hex Ç ü é â ä à å ç ê ë è ï î ì Ä Å É æ Æ ô ö ò û ù ÿ Ö Ü ǿ £ ¥ P, ƒ 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 80 81 82 83 84 85 86 87 88 89 8A 8B 8C 8D 8E 8F 90 91 92 93 94 95 96 97 98 99 9A 9B 9C 9D 9E 9F Sy mb ol á í ó ú ñ Ñ ā ō ¿ ⌐ ¬ ½ ¼ ¡ « » ░ ▒ ▓ │ ┤ ╡ ╢ ╖ ╡ ╣ ║ ╗ ╝ ╜ ╛ ┐ Dee Hex 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189 190 191 A0 Al A2 A3 A4 A5 A6 A7 A8 A9 AA AB AC AD AE AF B0 B1 B2 B3 B4 B5 B6 B7 B8 B9 BA BB BC BD BE BF Sy mb ol └ ┴ ┬ ├ ┤ ┼ ╞ ╟ ╚ ╔ ╩ ╦ ╠ ═ ╬ ╧ ╨ ╤ ╥ ╙ ╘ ╒ ╓ ╫ ╪ ┘ ┌ █ ▄ ▌ ▐ ▀ - 41 – Dec Hex Sym bol Dec Hex 192 193 194 195 196 197 198 199 200 201 202 203 204 205 206 207 208 209 210 211 212 213 214 215 216 217 218 219 220 221 222 223 C0 Cl C2 C3 C4 C5 C6 C7 C8 C9 CA CB CC CD CE CF DO Dl D2 D3 D4 D5 D6 D7 D8 D9 DA DB DC DD DE DF α β Γ π Σ б μ τ Φ Θ Ω δ ∞ Φ ε ∩ ≡ ± ≥ ≤ ∫ ÷ ≈ 224 225 226 227 228 229 230 231 232 233 234 235 236 237 238 239 240 241 242 243 244 245 246 247 248 249 250 251 252 253 254 255 E0 E1 E2 E3 E4 E5 E6 E7 E8 E9 EA EB EC ED EE EF F0 F1 F2 F3 F4 F5 F6 F7 F8 F9 FA FB FC FD FE FF ˚ • . √ η ² ▪

- 42. CHAPTER 1 NUMBER SYSTEMS AND CODES The Excess-3 Code Excess-3 is a digital code related to BCD that is derived by adding 3 to each decimal digit and then converting the result of that addition to 4-bit binary. Since no definite weights can be assigned to the four digit position, excess-3 is an unweighted code that has advantages in certain arithmetic operations. The excess-3 code for decimal 2 is 2+3=5 = (0101)2 The excess-3 code for each decimal digit is found by the same procedure. The entire code is shown in the following Table. Decimal Binary Excess-3 0 1 2 3 4 5 6 7 8 9 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 Notice that ten of the possible 16 code combinations are used in the excess-3 code. The six invalid combinations are 0000, 0001, 0010, 1101, 1110, and 1111. - 42 –

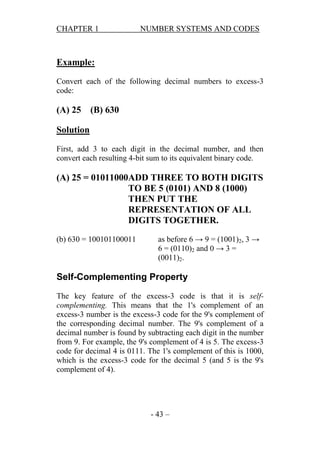

- 43. CHAPTER 1 NUMBER SYSTEMS AND CODES Example: Convert each of the following decimal numbers to excess-3 code: (A) 25 (B) 630 Solution First, add 3 to each digit in the decimal number, and then convert each resulting 4-bit sum to its equivalent binary code. (A) 25 = 01011000ADD THREE TO BOTH DIGITS TO BE 5 (0101) AND 8 (1000) THEN PUT THE REPRESENTATION OF ALL DIGITS TOGETHER. (b) 630 = 100101100011 as before 6 → 9 = (1001)2, 3 → 6 = (0110)2 and 0 → 3 = (0011)2. Self-Complementing Property The key feature of the excess-3 code is that it is selfcomplementing. This means that the 1's complement of an excess-3 number is the excess-3 code for the 9's complement of the corresponding decimal number. The 9's complement of a decimal number is found by subtracting each digit in the number from 9. For example, the 9's complement of 4 is 5. The excess-3 code for decimal 4 is 0111. The 1's complement of this is 1000, which is the excess-3 code for the decimal 5 (and 5 is the 9's complement of 4). - 43 –

- 44. CHAPTER 1 NUMBER SYSTEMS AND CODES The usefulness of the 9's complement and thus excess-3 stems from the fact that subtraction of a smaller decimal number from a larger one can be accomplished by adding the 9's complement (1's complement of the excess-3 code) of the subtrahend (in this case the smaller number) to the minuend and then adding the carry to the result. When subtracting a larger number from a smaller one, there is no carry, and the result is in 9's complement form and negative. This procedure has a distinct advantage over BCD in certain types of arithmetic logic. ERROR-DETECTION CODE Binary information can be transmitted from one location to another by electric wires or other communication medium. Any external noise introduced into the physical communication medium may change some of the bits from 0 to 1 or vice versa. The purpose of an error-detection code is to detect such bitreversal errors. One of the most common ways to achieve error detection is by means of a parity bit. A parity bit is an extra bit included with a message to make the total number of 1's transmitted either odd or even. A message of four bits and a parity bit P are shown in Table. If an odd parity is adopted, the P bit is chosen such that the total number of 1's is odd in the five bits that constitute the message and P. If an even parity is adopted, the P bit is chosen so that the total number of 1's in the five bits is even. Even parity being more common than odd parity. The parity bit is helpful in detecting errors during the transmission of information from one location to another. This is done in the following manner. An even parity bit is generated in the sending end for each message transmission. The message, together with the parity bit, is transmitted to its destination. The parity of the received data is checked. - 44 –

- 45. CHAPTER 1 NUMBER SYSTEMS AND CODES Parity bit Odd parity Message 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 P 1 0 0 1 0 1 1 0 0 1 1 0 1 0 0 Even parity Message 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 P 0 1 1 0 1 0 0 1 1 0 0 1 0 1 1 1 1111 0 - 45 –

- 46. CHAPTER 1 NUMBER SYSTEMS AND CODES QUESTIONS 1) Convert the following unsigned binary numbers to decimal, octal, hexadecimal and BCD if possible. i. 10110010011 ii 110000111000 iii 1000111011 2) Convert the following decimal numbers to binary, octal, hexadecimal and BCD. i. 739 ii 504 iii 861 3) What is the minimum number of bits to represent each of the following unsigned decimal numbers: 5110, 256,451228 and 700. 4) Add, multiply, subtract (A-B) and divide (A/B) each of the following binary numbers: i. A = 11010011 B = 1101 ii. A = 101101 B= 101 iii. A = 11101001 B = 1101 5) Represent each of the following decimal numbers (when possible) as an 8-bit number in each of the following formats: sign-magnitude, 1’s complement and 2’s complement. i 134 328 ii -54 iii -128 iv –150 v 6) Represent each of the following decimal numbers (when possible) as a 16-bit number in each of the following formats: sign-magnitude, 1’s complement and 2’s complement. i 134 328 ii -54 iii -128 vi 1023 iv –150 7) For each of the following signed decimal numbers, what is the minimum number of bits to represent - 46 – v

- 47. CHAPTER 1 NUMBER SYSTEMS AND CODES each of them if you are using: sign-magnitude format, 1’s complement and 2’s complement formats. i 134 328 ii -54 iii -128 vi 1023 iv –150 8) Determine the decimal value of the following signed binary numbers if they are expressed in signmagnitude, 1’s complement and 2’s complement. i 10010011 ii 01011010 iv 11010001 iii 10000110 9) If A is a binary number, let COMP(A) be the 2’s complement of A. prove that COMP(COMP(A)) = A. 10) Show that overflow occurs in 2’s complement adddition when the carry-out of the left-most column is the complement of the carry-out of the column next to the left-most. Use four different examples to prove it. 11) An imaginary frog hops half the distance to its goal with eqach jump. Its first jump is 32cm. How far will it have gone after four jumps? Express your answer in binary and in decimal. 12) How many different values can be formed with an eight-bit code? How many different values can be formed if the most significant bit is always zero? 13) There are about 3000 characters in written Japanese. How many bits minimum would it take to represent the set of Japanese characters? 14) Perform the following arithmetic operations by changing the decimal numbers to 8-bit binary in 2’s complement representation. Check your answer by - 47 – v

- 48. CHAPTER 1 NUMBER SYSTEMS AND CODES changing the output from 2’s complement to decimal. 9 – 15, -28 – 64, -127 + 93, -50 + 100 15) Perform the following operations if the numbers are in 2’s complement representation. Check for your answer by transforming to decimal. Check if there is an overflow. i 10010101 – 11010110 ii 01101100 + 10111111 iii 10100011 + 11001100 iv 00111100 + 01010101 16) What is meant by the overflow? 17) Perform the following operations if the numbers are in 2’s complement representation. Indicate if there is an overflow or not. Check for your answer by transforming to decimal. i 01110101 + 01101010 ii 10010000 – 01000111 iii 11010011 – 10110000 iv 01100000 - 00111111 18) Perform the following operations if the numbers are in 2’s complement representation. Extend all the numbers to be represented in 8-bits before performing the operation. Indicate if there is an overflow or not. Check for your answer by transforming to decimal. i 1011 – 0110 ii iii 0110 – 0101010 iv 1001 – 110010 v 10101 + 0110 vi - 48 – 010111 – 1111 10111 + 0111

- 49. CHAPTER 1 NUMBER SYSTEMS AND CODES vii 1110 + 0101010 viii 11001 + 100010 19) Add an 8th bit for the following binary numbers to act once as an even parity and another time as an odd parity. i 1010001 ii 1111000 iii 1101110 iv 1110111 20) Convert the following decimal numbers to BCD and excess-3 . 102, 897, 954, 045, 621 and 378 21) Writ the following phrase by representing each alphanumeric in ASCII code. Use hex numbers for each character. “The Little Brown Fox Jumps Over The Dog...1,2,3,4,5,6,7,8,9” 22) What is the special property of excess-3 code that makes it suitable to represent decimal numbers. 23) Determine the signed decimal value of 10010010 for each of the following representations: abcd- Sign-magnitude representation. 2’s complement representation. BCD representation. Excess representation 24) Determine the signed decimal value of 01010110 for each of the following representations: a- Sign-magnitude representation. - 49 – Lazy

- 50. CHAPTER 1 bc- NUMBER SYSTEMS AND CODES 2’s complement representation. BCD representation. 25) -Perform the subtraction of (36 – 99)10 using the 2’s complement representation. Verify your answer by converting into decimal. - 50 –

- 51. CHAPTER 2 LOGIC GATES CHAPTER 2 LOGIC GATES Boolean Variables & Truth Tables Boolean algebra differs in a major way from ordinary algebra in that boolean constants and variables are allowed to have only two possible values, 0 or 1. Boolean 0 and 1 do not represent actual numbers but instead represent the state of a voltage variable, or what is called its logic level. Some common representation of 0 and 1 is shown in the following diagram. LOGIC 0 False Off Low No Open Switch LOGIC 1 True On High Yes Close Switch In boolean algebra, there are three basic logic operations: OR, AND and NOT. These logic gates are digital circuits constructed from diodes, transistors, and resistors connected in such a way that the circuit output is the result of a basic logic operation (OR, AND, NOT) performed on the inputs. - 51 –

- 52. CHAPTER 2 LOGIC GATES Truth Table A truth table is a means for describing how a logic circuit's output depends on the logic levels present at the circuit's inputs. In the following two-inputs logic circuit, the table lists all possible combinations of logic levels present at inputs A and B along with the corresponding output level X. When either input A OR B is 1, the output X is 1. Therefore the function is an OR gate. OR Operation The expression X = A + B reads as "X equals A OR B". The + sign stands for the OR operation, not for ordinary addition. The OR operation produces a result of 1 when any of the input variable is 1. The OR operation produces a result of 0 only when all the input variables are 0. - 52 –

- 53. CHAPTER 2 LOGIC GATES An example of three input OR gate and its truth table is as follows: - 53 –

- 54. CHAPTER 2 LOGIC GATES With the OR operation, 1 + 1 = 1, 1+ 1 + 1 = 1 and so on. Timing Diagrams of OR gates A timing diagram is a graph that displays the relationship of two or more waveforms with respect to time. The following example explains the operation of an OR gate with pulsed inputs. Example If the two input waveforms A and B are applied to an OR gate, what is the resulting output waveform? An application: Alarm System A simplified portion of an intrusion detection and alarm system is shown. This system could be used for one room in a home a room with two windows and a door. The sensors are magnetic switches that produce a HIGH output when open and a LOW output when closed. As long as the windows and the door are secured, the switches are closed and all three of the OR gate inputs are LOW. When one of the windows or the door is opened, a HIGH is produced on that input to the OR gate and - 54 –

- 55. CHAPTER 2 LOGIC GATES the gate output goes HIGH. It then activates an alarm circuit to warn of the intrusion. AND Operation The expression X = A • B reads as "X equals A AND B". The multiplication sign stands for the AND operation, same for ordinary multiplication of 1s and 0s. The AND operation produces a result of 1 occurs only for the single case when all of the input variables are 1. The output is 0 for any case where one or more inputs are 0 - 55 –

- 56. CHAPTER 2 LOGIC GATES An example of three input AND gate and its truth table is as follows: - 56 –

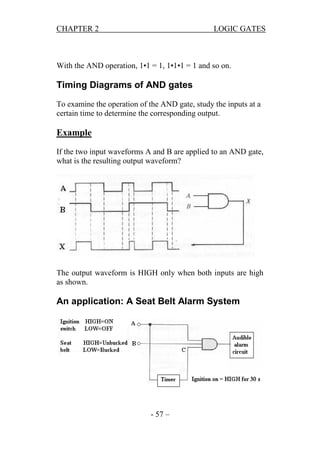

- 57. CHAPTER 2 LOGIC GATES With the AND operation, 1•1 = 1, 1•1•1 = 1 and so on. Timing Diagrams of AND gates To examine the operation of the AND gate, study the inputs at a certain time to determine the corresponding output. Example If the two input waveforms A and B are applied to an AND gate, what is the resulting output waveform? The output waveform is HIGH only when both inputs are high as shown. An application: A Seat Belt Alarm System - 57 –

- 58. CHAPTER 2 LOGIC GATES an AND gate is used in a simple car seat belt alarm system to detect when the ignition switch is on and the seat belt is unbuckled. If the ignition switch is on, a HIGH is produced on input A of the AND gate. If the seat belt is not properly buckled, a HIGH is produced on input B of the AND gate. Also, when the ignition switch is turned on, a timer is started that produces a HIGH on input C for 30 s. If all three conditions exist—that is, if the ignition is on and the seat belt is unbuckled and the timer is running—the output of the AND gate is HIGH, and an audible alarm is energized to remind the driver. NOT Operation The NOT operation is unlike the OR and AND operations in that it can be performed on a single input variable. For example, if the variable A is subjected to the NOT operation, the result x can be expressed as x = A' where the prime (') represents the NOT operation. This expression is read as: x equals NOT A x equals the inverse of A x equals the complement of A Each of these is in common usage and all indicate that the logic value of x = A' is opposite to the logic value of A. The truth table of the NOT operation is as follows: - 58 –

- 59. CHAPTER 2 LOGIC GATES 1' = 0 because NOT 1 is 0 0' = 1 because NOT 0 is 1 The NOT operation is also referred to as inversion or complementation, and these terms are used interchangeably. NOR Operation NOR and NAND gates are used extensively in digital circuitry. These gates combine the basic operations AND, OR and NOT, which make it relatively easy to describe then using Boolean Algebra. NOR is the same as the OR gate symbol except that it has a small circle on the output. This small circle represents the inversion operation. Therefore the output expression of the two input NOR gate is: X = ( A + B )' - 59 –

- 60. CHAPTER 2 LOGIC GATES An example of three input OR gate can be constructed by a NOR gate plus a NOT gate: Negative AND equivalent of a NOR gate The truth table of the NOR gate shows that a HIGH is produced on the gate output only if all of the inputs are LOW. From this viewpoint, the NOR gate can be used for an AND operation that - 60 –

- 61. CHAPTER 2 LOGIC GATES requires all LOW inputs to produce a HIGH output. This mode of operation is called negative-AND. The term negative means that the inputs are defined to be in the active state when LOW. In the operation of a 2-input NOR gate functioning as a negative-AND gate, output X is HIGH if both inputs/A and B are LOW. An application: An aircraft landing indicator Problem: In an aircraft, as part of its functional monitoring system, a circuit is required to indicate the status of the landing gear prior to landing. A green LED display turns on if all three gears are properly extended when the "gear down" switch has been activated in preparation for landing. A red LED display turns on if any of the gears fail to extend properly prior to landing. When a landing gear is extended, its sensor produces a LOW voltage. When a landing gear is retracted, its sensor produces a HIGH voltage. Implement a circuit to meet this requirement. Solution Power is applied to the circuit only when the "gear down" switch is activated. Use a NOR gate for each of the two requirements as shown in figure. One NOR gate operates as a negative-AND to detect a LOW from each of the three landing geal sensors. When all three of the gate inputs are LOW, the - 61 –

- 62. CHAPTER 2 LOGIC GATES three landing gear are properly extended and the resulting HIGH output from the negative-AND gate turns on the green LED display. The other NOR gate operates as a NOR to detect if one or more of the landing gear remain retracted when the "gear down" switch is activated. When one or more of the landing gear remain retracted, the resulting HIGH from the sensor is detected by the NOR gate, which produces a LOW output to turn on the red LED warning display. NAND Operation NAND is the same as the AND gate symbol except that it has a small circle on the output. This small circle represents the inversion operation. Therefore the output expression of the two input NAND gate is: - 62 –

- 63. CHAPTER 2 LOGIC GATES X = ( AB )' Negative OR Equivalent Operation of the NAND Gate In the NAND gate's operation, one or more LOW inputs produce a HIGH output. The previous truth table shows that output X is HIGH (1) when any of the inputs, A and B, are LOW (0). From this viewpoint, the NAND gate can be used for an OR operation that requires one or more LOW inputs to produce a HIGH output. This mode of operation is referred to as negative-OR. The term negative means that the inputs are defined to be in the active state when LOW. - 63 –

- 64. CHAPTER 2 LOGIC GATES In the operation of a 2-input NAND gate functioning as a negative-OR gate, output X is HIGH if either input A or input B is LOW, or if both A and Bare LOW. An application: A Manufacturing Plant Tank Indicator Problem: A manufacturing plant uses two tanks to store a certain liquid chemical that is required in a manufacturing process. Each tank has a sensor that detects when the chemical level drops to 25% of full. The sensors produce a 5 V level when the tanks are more than one-quarter full. When the volume of chemical in a tank drops to one-quarter full, the sensor puts out a 0 V level. It is required that a single green light-emitting diode (LED) on an indicator panel show when both tanks are more than one quarter full. Show how a NAND gate can be used to implement this function. Solution: As long as both sensor outputs are HIGH, indicating that both tanks are more than one quarter full, the NAND gate output is LOW. The green LED circuit is arranged so that a low voltage turns it ON. - 64 –

- 65. CHAPTER 2 LOGIC GATES THE EXCLUSIVE-OR AND EXCLUSIVENOR GATES The exclusive-OR and exclusive-NOR gates are formed by the combination of other logic gates you have already studied. Because of their versatile range of applications, they are treated as basic gates and given their own symbols. The Exclusive- OR Gate The symbol of exclusive-OR (XOR for short) is shown along with its truth table. Inputs A 0 0 1 1 - 65 – output B 0 1 0 1 X 0 1 1 0

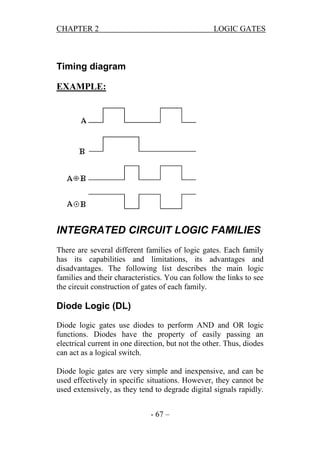

- 66. CHAPTER 2 LOGIC GATES The symbol used to express the XOR is: X = AB. From the truth table, the operation of the XOR can be summarized as: In an XOR gate operation, output X is HIGH if input A is LOW and input B is HIGH, or if input A is HIGH and input B is LOW; X is LOW if A and B are both HIGH or both LOW. The Exclusive-NOR Gate The symbol of exclusive-NOR (XNOR for short or equivalence) is shown along with its truth table. Inputs A 0 0 1 1 output B 0 1 0 1 X 1 0 0 1 The symbol used to express the XNOR is: X = AB. From the truth table, the operation of the XNOR can be summarized as: In an XNOR gate operation, output X is LOW if input A is LOW and input B is HIGH, or if input A is HIGH and input B is LOW; X is HIGH if A and B are both HIGH or both LOW. It is obvious that the XNOR is the complement of the XOR which is the reason of the bubble in the symbol of the XNOR. - 66 –

- 67. CHAPTER 2 LOGIC GATES Timing diagram EXAMPLE: INTEGRATED CIRCUIT LOGIC FAMILIES There are several different families of logic gates. Each family has its capabilities and limitations, its advantages and disadvantages. The following list describes the main logic families and their characteristics. You can follow the links to see the circuit construction of gates of each family. Diode Logic (DL) Diode logic gates use diodes to perform AND and OR logic functions. Diodes have the property of easily passing an electrical current in one direction, but not the other. Thus, diodes can act as a logical switch. Diode logic gates are very simple and inexpensive, and can be used effectively in specific situations. However, they cannot be used extensively, as they tend to degrade digital signals rapidly. - 67 –

- 68. CHAPTER 2 LOGIC GATES In addition, they cannot perform a NOT function, so their usefulness is quite limited. In the figure above, you see a basic Diode Logic OR gate. We'll assume that a logic 1 is represented by +5 volts, and a logic 0 is represented by ground, or zero volts. In this figure, if both inputs are left unconnected or are both at logic 0, output Z will also be held at zero volts by the resistor, and will thus be a logic 0 as well. However, if either input is raised to +5 volts, its diode will become forward biased and will therefore conduct. This in turn will force the output up to logic 1. If both inputs are logic 1, the output will still be logic 1. Hence, this gate correctly performs a logical OR function. The figure above shows the equivalent AND gate. We use the same logic levels, but the diodes are reversed and the resistor is - 68 –

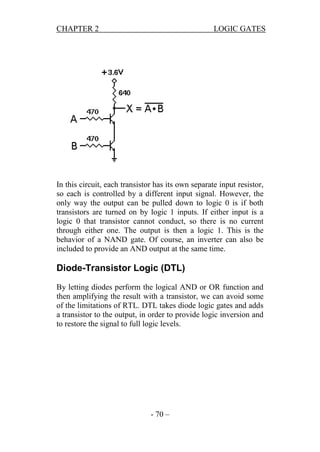

- 69. CHAPTER 2 LOGIC GATES set to pull the output voltage up to a logic 1 state. For this example, +V = +5 volts, although other voltages can just as easily be used. Now, if both inputs are unconnected or if they are both at logic 1, output Z will be at logic 1. If either input is grounded (logic 0), that diode will conduct and will pull the output down to logic 0 as well. Both inputs must be logic 1 in order for the output to be logic 1, so this circuit performs the logical AND function. Resistor-Transistor Logic (RTL) Resistor-transistor logic gates use Transistors to combine multiple input signals, which also amplify and invert the resulting combined signal. Often an additional transistor is included to re-invert the output signal. This combination provides clean output signals and either inversion or noninversion as needed. RTL gates are almost as simple as DL gates, and remain inexpensive. They also are handy because both normal and inverted signals are often available. However, they do draw a significant amount of current from the power supply for each gate. Another limitation is that RTL gates cannot switch at the high speeds used by today's computers, although they are still useful in slower applications. - 69 –

- 70. CHAPTER 2 LOGIC GATES In this circuit, each transistor has its own separate input resistor, so each is controlled by a different input signal. However, the only way the output can be pulled down to logic 0 is if both transistors are turned on by logic 1 inputs. If either input is a logic 0 that transistor cannot conduct, so there is no current through either one. The output is then a logic 1. This is the behavior of a NAND gate. Of course, an inverter can also be included to provide an AND output at the same time. Diode-Transistor Logic (DTL) By letting diodes perform the logical AND or OR function and then amplifying the result with a transistor, we can avoid some of the limitations of RTL. DTL takes diode logic gates and adds a transistor to the output, in order to provide logic inversion and to restore the signal to full logic levels. - 70 –

- 71. CHAPTER 2 LOGIC GATES The above gate t is a DL OR gate followed by an inverter. The OR function is still performed by the diodes. However, regardless of the number of logic 1 inputs, there is certain to be a high enough input voltage to drive the transistor into saturation. Only if all inputs are logic 0 will the transistor be held off. Thus, this circuit performs a NOR function. The advantage of this circuit over its RTL equivalent is that the OR logic is performed by the diodes, not by resistors. Therefore there is no interaction between different inputs, and any number of diodes may be used. A disadvantage of this circuit is the input resistor to the transistor. Its presence tends to slow the circuit down, thus limiting the speed at which the transistor is able to switch states. Transistor-Transistor Logic (TTL) The physical construction of integrated circuits made it more effective to replace all the input diodes in a DTL gate with a transistor, built with multiple emitters. The result is transistor- - 71 –

- 72. CHAPTER 2 LOGIC GATES transistor logic, which became the standard logic circuit in most applications for a number of years. As the state of the art improved, TTL integrated circuits were adapted slightly to handle a wider range of requirements, but their basic functions remained the same. These devices comprise the 7400 family of digital ICs. The preceding figure shows an inverter designed with TTL logic. - 72 –

- 73. CHAPTER 2 LOGIC GATES The preceding figure shows a 4-input NAND gate designed with TTL logic. Emitter-Coupled Logic (ECL) Also known as Current Mode Logic (CML), ECL gates are specifically designed to operate at extremely high speeds, by avoiding the "lag" inherent when transistors are allowed to become saturated. Because of this, however, these gates demand substantial amounts of electrical current to operate correctly. CMOS Logic One factor is common to all of the logic families we have listed above: they use significant amounts of electrical power. Many applications, especially portable, battery-powered ones, require - 73 –

- 74. CHAPTER 2 LOGIC GATES that the use of power be absolutely minimized. To accomplish this, the CMOS (Complementary Metal-Oxide-Semiconductor) logic family was developed. This family uses enhancementmode MOSFETs as its transistors, and is so designed that it requires almost no current to operate. CMOS gates are, however, severely limited in their speed of operation. Nevertheless, they are highly useful and effective in a wide range of battery-powered applications. CMOS logic is a newer technology, based on the use of complementary MOS transistors to perform logic functions with almost no current required. This makes these gates very useful in battery-powered applications. The fact that they will work with supply voltages as low as 3 volts and as high as 15 volts is also very helpful. CMOS gates are all based on the fundamental inverter circuit shown above. Note that both transistors are enhancement-mode MOSFETs; one N-channel with its source grounded, and one Pchannel with its source connected to +V. Their gates are connected together to form the input, and their drains are connected together to form the output. The two MOSFETs are designed to have matching characteristics. Thus, they are complementary to each other. - 74 –

- 75. CHAPTER 2 LOGIC GATES When off, their resistance is effectively infinite; when on, their channel resistance is about 200 . Since the gate is essentially an open circuit it draws no current, and the output voltage will be equal to either ground or to the power supply voltage, depending on which transistor is conducting. When input A is grounded (logic 0), the N-channel MOSFET is unbiased, and therefore has no channel enhanced within itself. It is an open circuit, and therefore leaves the output line disconnected from ground. At the same time, the P-channel MOSFET is forward biased, so it has a channel enhanced within itself. This channel has a resistance of about 200 , connecting the output line to the +V supply. This pulls the output up to +V (logic 1). When input A is at +V (logic 1), the P-channel MOSFET is off and the N-channel MOSFET is on, thus pulling the output down to ground (logic 0). Thus, this circuit correctly performs logic inversion, and at the same time provides active pull-up and pulldown, according to the output state. - 75 –

- 76. CHAPTER 2 LOGIC GATES This concept can be expanded into NOR and NAND structures by combining inverters in a partially series, partially parallel structure Most logic families share a common characteristic: their inputs require a certain amount of current in order to operate correctly. CMOS gates work a bit differently, but still represent a capacitance that must be charged or discharged when the input changes state. The current required to drive any input must come from the output supplying the logic signal. Therefore, we need to know how much current an input requires, and how much current an output can reliably supply, in order to determine how many inputs may be connected to a single output. However, making such calculations can be tedious, and can bog down logic circuit design. Therefore, we use a different technique. Rather than working constantly with actual currents, we determine the amount of current required to drive one standard input, and designate that as a standard load on any output. Now we can define the number of standard loads a given output can drive, and identify it that way. Unfortunately, some - 76 –

- 77. CHAPTER 2 LOGIC GATES inputs for specialized circuits require more than the usual input current, and some gates, known as buffers, are deliberately designed to be able to drive more inputs than usual. For an easy way to define input current requirements and output drive capabilities, we define two new terms: Fan-in The number of standard loads drawn by an input to ensure reliable operation. Most inputs have a fan-in of 1. Fan-out The number of standard loads that can be reliably driven by an output, without causing the output voltage to shift out of its legal range of values. Comparison of performance characteristics of CMOS, TTL and ECL logic gates. Technology Device series Power dissipation: Static CMOS (silicon gate) 74HC At 100 kHz CMOS TTL TTL TTL TTL TTL ECL (metal std LS S ALS AS gate) 4000B 74 74LS 74S 74ALS 74AS 10KH 1 uW 10 mW 10 mW 10 ns 10 2 mW 2 mW 10 ns 19 mW 19 mW 3 ns 1 mW 20 20 20 0.17 mW Propagation 8 ns delay time Fan-out 0.1 mW 50 ns Std : standard LS: Low power Schottky - 77 – 1 mW 4 ns 8.5 mW 8.5 mW 1.5 ns 40 S: Schottky 25 mW 25 mW 1 ns

- 78. CHAPTER 2 LOGIC GATES ALS: Advanced Low power Schottky AS: Advanced Schottky QUESTIONS Choose the correct answers in the following questions. 1. Boolean algebra is different from ordinary algebra in which way? i. Boolean algebra can represent more than 1 discrete level between 0 and 1 ii. Boolean algebra have only 2 discrete levels: 0 and 1 iii. Boolean algebra can describe up to 3 levels of logic levels iv. They are actually the same v. NA The following 2 questions are referred to the below image: 2. What is the output X if both inputs A and B are 0? i. ii. iii. iv. 0 1 I don’t know NA 3. What is the output X if A=1 and B=0? - 78 –

- 79. CHAPTER 2 i. ii. iii. iv. LOGIC GATES 0 1 I don’t know NA 4. For a three inputs (A,B C) OR gate, what inputs are needed if output=0? i. ii. iii. iv. v. A=0, B=0, C=1 A=0, B=1, C=0 A=1, B=1, C=1 A=0, B=0,C=0 NA The following 2 questions are referred to the below image: 5. What is the output X if input A=1, B=0 and C=1? i. ii. iii. iv. 0 1 I don’t know NA 6. What inputs are needed if output=1? i. ii. iii. iv. v. A=0, B=0, C=0 A=1, B=0, C=1 A=0, B=1, C=0 A=1, B=1,C=1 NA - 79 –

- 80. CHAPTER 2 LOGIC GATES The following 2 questions are related to the below image: 7. What is the ouput of the above gate if input A=0, B=1? v. vi. vii. viii. 0 1 not sure NA 8. What are the value of the inputs if output=1? i. ii. iii. iv. v. A=0, B=0 A=0, B=1 A=1, B=0 A=1, B=1 I don't know The following 2 questions are related to the below image: 9. What are the values of the inputs if output=0? i. ii. iii. iv. v. A=0, B=0 A=0, B=1 A=1, B=0 A=1, B=1 I don't know - 80 –

- 81. CHAPTER 2 LOGIC GATES 10. For the truth table below, what type of logic gate is it? i. ii. iii. iv. v. 3 Inputs OR 3 Inputs AND 3 Inputs NOR 3 Inputs NAND Not sure 11. If the two input waveforms A and B are applied to an AND gate, draw a timing diagram for the resulting output waveform? 12. If the three input waveforms A, B and C are applied to a three input AND gate, draw a timing diagram for the resulting output waveform? - 81 –

- 82. CHAPTER 2 LOGIC GATES 13. Repeat problems 11 and 12 using OR gates. 14. Repeat problems 11 and 12 using NOR gates. 15. Repeat problems 11 and 12 using NAND gates. 16. Repeat problem 11 using XOR gate. 17. Repeat problem 11 using XNOR gate. 18. Prove that AB = A'B +AB'. 19. Prove that AB = AB +A'B'. 20. . In the comparison of certain logic devices, it is noted that the power dissipation for one particular type increases as the frequency increases. Is the device TTL or CMOS? 21. Using the table which compares logic families, determine which logic series offers the best performance considering both switching speed and power dissipation at 100 kHz. Note: Find the speed-power product of each and compare the results. 22. Sensors are used to monitor the pressure and the temperature of a chemical solution stored in a vat. The circuitry for each sensor produces a HIGH voltage when a specified maximum value is exceeded. An alarm requiring a LOW voltage input must be activated when either the pressure or the temperature is excessive. Design a circuit for this application? 23. Modify the logic circuit for the intrusion alarm introduced in this chapter so that two additional rooms, each with two windows and one door, can be protected - 82 –

- 83. CHAPTER 2 LOGIC GATES - 83 –

- 84. CHAPTER3 BOOLEAN ALGEBRA CHAPTER 3 Boolean Algebra Describing Logic Circuits Algebraically Any logic circuit, no matter how complex, may be completely described using the Boolean operations, because the OR gate, AND gate, and NOT circuit are the basic building blocks of digital systems. This is an example of the circuit using Boolean expression: If an expression contains both AND and OR operations, the AND operations are performed first (X=AB+C : AB is performed first), unless there are parentheses in the expression, in which case the operation inside the parentheses is to be performed first (X=(A+B)+C : A+B is performed first). Circuits containing Inverters Whenever an inverter is present in a logic-circuit diagram, its output expression is simply equal to the input expression with a prime (') over it. - 84 –

- 85. CHAPTER3 BOOLEAN ALGEBRA Evaluating Logic Circuit Outputs Once the Boolean expression for a circuit output has been obtained, the output logic level can be determined for any set of input levels. This are two examples of the evaluating logic circuit output: Let A=0, B=1, C=1, D=1 X = A'BC (A+D)' = 0'•1•1• (0+1)' = 1 •1•1• (1)' = 1 •1•1• 0 =0 Let A=0, B=0, C=1, D=1, E=1 X = [D+ ((A+B)C)'] • E = [1 + ((0+0)1 )'] • 1 = [1 + (0•1)'] • 1 = [1+ 0'] •1 = [1+ 1 ] • 1 =1 - 85 –

- 86. CHAPTER3 BOOLEAN ALGEBRA In general, the following rules must always be followed when evaluating a Boolean expression: i. ii. iii. iv. First, perform all inversions of single terms; that is, 0 = 1 or 1 = 0. Then perform all operations within parentheses. Perform an AND operation before an OR operation unless parentheses indicate otherwise. If an expression has a bar over it, perform the operations of the expression first and then invert the result. Determining Output Level from a Diagram The output logic level for given input levels can also be determined directly from the circuit diagram without using the Boolean expression. - 86 –

- 87. CHAPTER3 BOOLEAN ALGEBRA Implementing Circuits From Boolean Expression If the operation of a circuit is defined by a Boolean expression, a logiccircuit diagram can he implemented directly from that expression. Suppose that we wanted to construct a circuit whose output is y = AC+BC' + A'BC. This Boolean expression contains three terms (AC, BC', A'BC), which are ORed together. This tells us that a three-input OR gate is required with inputs that are equal to AC, BC', and A'BC, respectively. Each OR-gate input is an AND product term, which means that an AND gate with appropriate inputs can be used to generate each of these terms. Note the use of inverters to produce the A' and C' terms required in the expression. - 87 –

- 88. CHAPTER3 BOOLEAN ALGEBRA Boolean Theorems Investigating the various Boolean theorems (rules) can help us to simplify logic expressions and logic circuits. - 88 –

- 89. CHAPTER3 BOOLEAN ALGEBRA Multivariable Theorems The theorems presented below involve more than one variable: (9) (10) (11) (12) (13a) )13b) (13c) (14) (15) (16) (17) x + y = y + x (commutative law) x • y = y • x (commutative law) x+ (y+z) = (x+y) +z = x+y+z (associative law) x (yz) = (xy) z = xyz (associative law) x (y+z) = xy + xz (distributive law) x + yz = (x + y) (x + z) (distributive law) (w+x)(y+z) = wy + xy + wz + xz x + xy = x [proof see below] x + x'y = x + y (x +y)(x + z) = x +yz x + xy = x (absorption) Proof of (14) x + xy = x (1+y) = x • 1 [using theorem (6)] = x [using theorem (2)] x + x’y = ( x + x’) (x + y) [theorem 13b] = 1 (x +y) = (x + y) Proof of (15) Proof of (16) - 89 –

- 90. CHAPTER3 BOOLEAN ALGEBRA (x +y)(x + z) =xx + xz + yx + yz = x + xz + yx + yz = x (1+z+y) +yz = x . 1 + yz = x + yz EXAMPLE The logic circuit shown in Figure is used to turn on a warning bell at X based on the input conditions at A, B, and C. A simplified equivalent circuit that will perform the same function can be formed by using Boolean algebra. Write the equation of the circuit in Figure, simplify the equation, and draw the logic circuit of the simplified equation. Solution: The Boolean equation for X is X = B(A + C) + C = BA + BC + C = BA + C(B + 1) = BA+C.1 = BA + C X = BA + C The logic circuit of the simplified equation is shown in Figure. - 90 –

- 91. CHAPTER3 BOOLEAN ALGEBRA DeMorgan's Theorem DeMorgan's theorems are extremely useful in simplifying expressions in which a product or sum of variables is inverted. The two theorems are: (18) (x+y)' = x' • y' (19) (x•y)' = x' + y' Theorem (18) says that when the OR sum of two variables is inverted, this is the same as inverting each variable individually and then ANDing these inverted variables. Theorem (19) says that when the AND product of two variables is inverted, this is the same as inverting each variable individually and then ORing them. Example X = [(A'+C) • (B+D')]' = (A'+C)' + (B+D')' = (AC') + (B'D) = AC' + B'D - 91 –

- 92. CHAPTER3 BOOLEAN ALGEBRA Three Variables DeMorgan's Theorem (20) (x+y+z)' = x' • y' • z' (21) (xyz)' = x' + y' + z' Implications of DeMorgan's Theorem (x+y)' = x' • y' (x•y)' = x' + y' - 92 –

- 93. CHAPTER3 BOOLEAN ALGEBRA EXAMPLE: Apply DeMorgan’s theorems to each of the following expressions: (a) (A B C)D (b) ABC DEF (c) AB CD EF - 93 –

- 94. CHAPTER3 BOOLEAN ALGEBRA solution: (a) (A B C)D = A B C D = ABC D (b) ABC DEF = (ABC)(DEF) (A B C)(D E F) (c) AB CD EF = (AB)(CD)(EF) = (A B)(C D)(E F) Universality of NAND & NOR Gates It is possible to implement any logic expression using only NAND gates and no other type of gate. This is because NAND gates, in the proper combination, can be used to perform each of the Boolean operations OR, AND, and INVERT. - 94 –

- 95. CHAPTER3 BOOLEAN ALGEBRA In a similar manner, it can be shown that NOR gates can be arranged to implement any of the Boolean operations. - 95 –

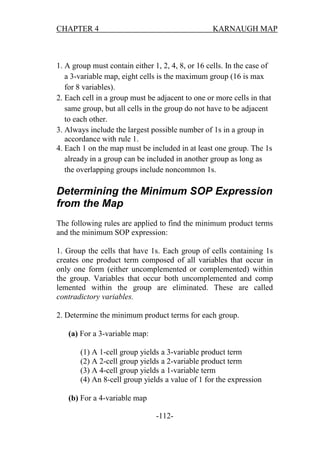

- 96. CHAPTER3 BOOLEAN ALGEBRA Alternate Logic Gate Representations The left side of the illustration shows the standard symbol for each logic gate, and the right side shows the alternate symbol. The alternate symbol for each gate is obtained from the standard symbol by doing the following: 1. Invert each input and output of the standard symbol. This is done by adding bubbles (small circles) on input and output lines that do not have bubbles, and by removing bubbles that are already there. 2. Change the operation symbol from AND to OR, or from OR to AND. (In the special case of the INVERTER, the operation symbol is not changed.) Several points should be stressed regarding the logic symbol equivalences: 1. The equivalences are valid for gates with any number of inputs. 2. None of the standard symbols have bubbles on their inputs, and all the alternate symbols do. 3. The standard and alternate symbols for each gate represent the same physical circuit: there is no difference in the circuits represented by the two symbols. - 96 –